# HARDWARE MANUAL

# MICROCOMPUTERS MCROCOMPUTERS

MICHOLDSPHTERS

Publication Number 6500-10A

# MCS6500

## MICROCOMPUTER FAMILY

# HARDWARE MANUAL

# **JANUARY 1976**

The information in this manual has been reviewed and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. The material in this manual is for informational purposes only and is subject to change without notice.

Second Edition ©MOS TECHNOLOGY, INC. 1976 "All Rights Reserved"

-

MOS TECHNOLOGY, INC. 950 Rittenhouse Road Norristown, PA. 19401

Revision A

## PREFACE

The MOS Technology, Inc. MCS6500 Microcomputer System offering combines the best features of second generation families into a product line that is both a price and performance leader. A growing array of products and a unique microprocessor <u>family</u> provide the customer with answers to the complex design problems confronting today's programmers and designers.

Integrated circuit fabrication techniques have moved microprocessors to the forefront of complex, sophisticated components. The MCS6500 family benefits from an advanced but proven process technology; N-Channel, Silicon Gate, and Depletion Loads are the key elements providing the high performance characteristics obtainable in the single supply 5-volt system usage of the MCS6500 family.

The N-Channel, Silicon Gate technology is enhanced by use of Depletion Loads which provides greater speed, lower power and smaller chip size than previous processing approaches. Ion Implementation techniques are basic elements in providing control and stability of all processing parameters necessary to achieve the electrical characteristics of the MCS6500 product line. These characteristics provide a price/performance combination which establishes the MCS6500 family as the product offering best meeting the economic and technical demands of today's system designs.

A word of explanation is in order regarding the MCS6500 product line, since the concept of "Microprocessor Family" is indeed unique to the industry. It is helpful to understand the basic product structure of the MCS6500 family.

The MCS650X Series represents the Microprocessor Family. Within this family will exist a series of 8-bit devices offering a wide range of options and capabilities for the customer. For the single-application customer, a varied selection of devices is at his disposal in choosing the one that best meets his specific needs. The "Microprocessor Family" concept has an even greater impact

-ii-

to the user who has a variety of applications, each of which can best be served by a specific member of the family. It is important to this user that all of the different microprocessors he selects maintain compatibility--both hardware (from the standpoint of bus and electrical specifications) <u>and</u> software. The MCS650X product line is the first microprocessor family to achieve such a level of compatibility because it was indeed conceptualized as a totally software and hardware compatible family of microprocessors offering a range of performance options from which the designer can select. The MCS6501 and MCS6502 are the first two 40-pin members of the MCS650X family, each offering 65K bytes of addressable memory. The MCS6503, MCS6504 and MCS6505 are the first 28-pin versions with various options of addressing capability and control functions from which to choose.

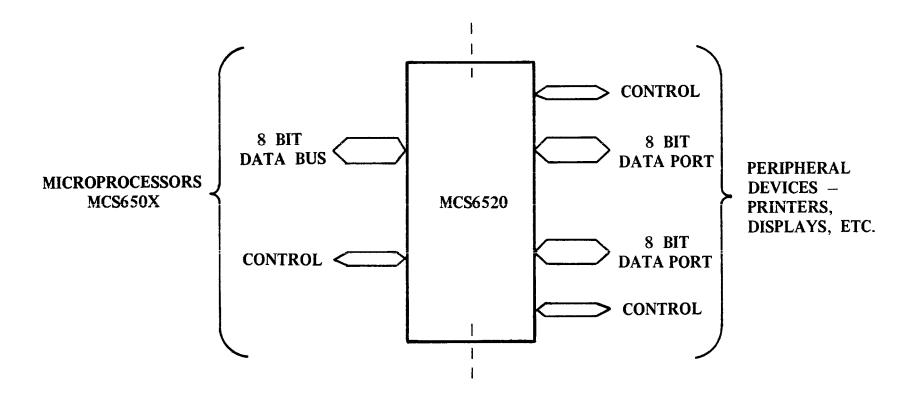

The MCS652X Series represents Peripheral Input/Output devices, the first being the MCS652O which is a direct replacement for the Motorola MC682O Peripheral Interface Adapter (PIA). Subsequent members of this series will include devices with expanded I/O capabilities.

The MCS653X Series represents combinational devices--those consisting of various tradeoffs in RAM, ROM, I/O, and Timing. The first of these is the MCS6530 which contains 1K bytes of ROM, 64 bytes of RAM, an Interval Timer and 16 I/O lines. Subsequent products in this series will provide the customer with different combinations and new implementations of I/O, Timing and Memory.

The MCS654X Series represents Read Only Memories specifically tailored to meet the needs of large program storage required in many of the applications of the MCS6500 family of products. The first of these will be a 16K (2K x 8) ROM, the MCS6540.

All of the MCS6500 product lines outlined utilize the same fabrication techniques and meet identical electrical specifications. With this family of compatible products the designer of today has at his disposal the elements necessary to develop a system configured to meet the most demanding tasks.

Complementing the MCS6500 family is a selection of Random Access Memories totally compatible with the microcomputer family. The first of these will be the MCS6102, a 2102 equivalent, and the MCS6111, a 2111 equivalent.

To allow for minimum I/O cost and maximum user flexibility, all of the MCS6500 products are compatible with the M6800 bus structure.

-iii-

Chapter 1 of this manual introduces the reader to the MCS6500 Microcomputer System. It includes an introduction to terminology, an explanation of system components of a general microcomputer system, and then discusses the components of the MCS6500 Product Family.

Chapter 2 is applications-oriented, with a discussion of system configuration, the I/O port, handshaking and specific examples on interrupt prioritizing, interfacing with peripherals, direct memory addressing techniques, and control of memories in the system.

Chapter 3 is directed at the important task of bringing up a system. It takes the reader through a step-by-step procedure in analyzing, statically and dynamically, the basic elements of the system to assist the user in a smooth transition from a conceptual system to an operational one.

# TABLE OF CONTENTS

## CHAPTER 1 THE MCS6500 MICROCOMPUTER SYSTEM

| 1.0 Designing with Microcomputer Systems                 |

|----------------------------------------------------------|

| 1.1 Introduction to Microcomputer Systems 4              |

| 1.1.1 Organization of a Microcomputer System 4           |

| 1.1.2 Basic Operation                                    |

| 1.1.3 Addressing Terms and Concepts 4                    |

| 1.1.3.1 Bit                                              |

| 1.1.3.2 Address Space                                    |

| 1.1.3.3 The Address Page                                 |

| 1.1.4 System Components                                  |

| 1.1.4.1 Clock Generator                                  |

| 1.1.4.2 Program Memory                                   |

| 1.1.4.3 Data Memory                                      |

| 1.1.4.4 Input/Output Devices                             |

| 1.1.4.5 The Microprocessor                               |

|                                                          |

| 1.2 Introduction to the MCS650X Microprocessor Family 12 |

|                                                          |

| 1.2.1 The MCS6501                                        |

| 1.2.2 The MCS6502                                        |

| 1.2.3 The MCS6503, MCS6504 and MCS6505                   |

|                                                          |

| 1.3 MCS6500 System Concepts                              |

|                                                          |

| 1.3.1 Bus Structure                                      |

| 1.3.2 Processor Interrupts                               |

| 1.3.2.1 Applications for Interrupts                      |

| 1.3.2.2 Interrupt Prioritizing                           |

| 1.3.2.3 System Interconnect for Interrupts               |

| •                                                        |

|                                                          |

|                                                          |

| 1.3.2.6 Non-Maskable Interrupt (NMI)                     |

| 1.3.3 System Reset                                       |

|   | 1.4 The Microprocessors                                |

|---|--------------------------------------------------------|

|   | 1.4.1 The MCS6501                                      |

|   | 1.4.1.1 Introduction                                   |

|   | 1.4.1.2 The MCS6501 Pinouts                            |

|   | 1.4.1.2.1 Vcc, VssSupply Lines                         |

|   | 1.4.1.2.2 ABOO - AB15Address Bus                       |

|   | 1.4.1.2.3 DBO - DB7Data Bus                            |

|   | 1.4.1.2.4 R/WRead/Write                                |

|   | 1.4.1.2.5 DBEData Bus Enable                           |

|   | 1.4.1.2.6 VMAValid Memory Address                      |

|   | 1.4.1.2.7 BABus Available                              |

|   | 1.4.1.2.8 RDYReady                                     |

|   | 1.4.1.2.9 NMINon-Maskable Interrupt                    |

|   | 1.4.1.2.10 IRQInterrupt Request                        |

|   | 1.4.1.2.11 RESReset                                    |

| , | 1.4.2 The MCS6502                                      |

|   | 1.4.2.1 Product Characteristics                        |

|   | 1.4.2.2 Device TimingRequirements and Generation 41    |

|   | 1.4.2.3 SYNC Signal                                    |

|   |                                                        |

|   | 1.4.2.4 S.OSet Overflow                                |

|   | 1.4.3 The MCS6503, MCS6504 and MCS6505                 |

|   | 1.5 Peripheral Interface DeviceMCS6520 50              |

|   | 1.5.1 Introduction                                     |

|   | 1.5.2 Organization of the MCS6520                      |

|   | 1.5.2.1 Data Input Register                            |

|   | 1.5.2.2 Control Registers (CRA and CRB)                |

|   | 1.5.2.3 Data Direction Registers (DDRA, DDRB) 55       |

|   | 1.5.2.4 Peripheral Output Registers (ORA, ORB) 55      |

|   | 1.5.2.5 Interrupt Status Control                       |

|   | 1.5.2.6 Peripheral Interface Buffers (A, B) and Data   |

|   | Bus Buffers (DBB)                                      |

|   | 1.5.3 Interface Between MCS6520 and the MCS650X Family |

|   | of Microprocessors                                     |

|   | 1.5.3.1 Data Bus (DO-D7)                               |

|   | 1.5.3.2 Enable (E)                                     |

|   | 1.5.3.3 Read/Write (R/W)                               |

|   | 1.5.3.4 Chip-Select Lines (CS1, CS2, CS3)              |

|   | 1.5.3.5 Register-Select Lines (RS, RS1)                |

|   | 1.5.3.5.1 Reading the Peripheral A I/O Port            |

|   | 1.5.3.5.2 Reading the Peripheral B I/O Port            |

|   | 1.5.3.6 Reset (RES)                                    |

|   | 1.5.3.7 Interrupt Request Line (IRQA, IRQB)            |

|   | 1.5.3.7.1 Control of TRQA                              |

|   | 1.5.3.7.2 Control of IRQB                              |

|   |                                                        |

,

| 1.5.4 Interface Between MCS6520 and Peripheral Devices                                                                                  | • | • | 64  |

|-----------------------------------------------------------------------------------------------------------------------------------------|---|---|-----|

| 1.5.4.1 Peripheral I/O Ports                                                                                                            | • | • | 64  |

| 1.5.4.1.1 Peripheral A I/O Port (PAØ-PA7)                                                                                               |   |   |     |

| 1.5.4.1.2 Peripheral B I/O Port (PBØ-PB7)                                                                                               |   |   |     |

| 1.5.4.2 Interrupt Input/Peripheral Control Lines (CA1,                                                                                  |   |   | •   |

| CA2, CB1, CB2)                                                                                                                          |   | • | 66  |

| 1.5.4.2.1 Peripheral A Interrupt Input/Peripheral                                                                                       |   |   |     |

| Control Lines (CB1, CB2)                                                                                                                | • | • | 66  |

| 1.5.4.2.2 Peripheral B Interrupt Input/Peripheral                                                                                       |   |   |     |

| Control Lines (CB1, CB2)                                                                                                                |   |   | 67  |

| 1.5.5 Summary of MCS6520 Operation.                                                                                                     |   |   |     |

| 1.5.5.1 Control Register Operation.                                                                                                     |   |   |     |

| 1.5.5.2 MCS6520 Operation in MC6500 Systems                                                                                             |   |   |     |

| 1.J.J.Z MCS0J20 Operation in MC0J00 Systems                                                                                             | • | • | /0  |

| 1.6 Peripheral Interface/Memory DeviceMCS6530                                                                                           |   |   | 71  |

| 1.0 Feripheral incertace/memory bevice mosoboo                                                                                          | • | • | 1 1 |

| 1.6.1 Introduction                                                                                                                      |   |   | 71  |

| 1.6.2 Pinout Description.                                                                                                               |   |   |     |

| 1.6.2.1 Reset (RES) $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                 |   |   |     |

|                                                                                                                                         |   |   |     |

| 1.6.2.2 Input Clock $\dots \dots \dots$ | • | • | 73  |

| 1.6.2.3 Read/Write $(R/W)$                                                                                                              | • | • | 73  |

| 1.6.2.4 Interrupt Request (IRQ)                                                                                                         |   |   |     |

| 1.6.2.5 Data Bus (D-D7)                                                                                                                 | • | • | 13  |

| 1.6.2.6 Peripheral Data Ports                                                                                                           | • | • | 13  |

| 1.6.2.7 Address Lines (A0-A9)                                                                                                           |   |   |     |

| 1.6.3 Internal Organization                                                                                                             |   |   |     |

| 1.6.3.1 ROM1K Byte (8K Bits)                                                                                                            |   |   |     |

| 1.6.3.2 RAM64 Bytes (512 Bits)                                                                                                          | • | ٠ | 76  |

| 1.6.3.3 Internal Peripheral Registers                                                                                                   |   |   |     |

| 1.6.3.4 Interval Timer                                                                                                                  |   |   |     |

| 1.6.4 Addressing                                                                                                                        | • | • | 78  |

| 1.6.4.1 One-Chip Addressing                                                                                                             |   |   |     |

| 1.6.4.2 Seven-Chip Addressing                                                                                                           |   |   |     |

| 1.6.4.3 I/O RegisterTimer Addressing                                                                                                    | • | • | 80  |

|                                                                                                                                         |   |   |     |

## CHAPTER 2 CONFIGURING THE MICROCOMPUTER SYSTEM

| <ul><li>2.2.5 Handshaking.</li><li>2.2.5.1 Handshaking on Data Transfers from the Processor</li><li>2.2.5.2 Handshaking on Data Transfers into the Processor</li></ul> | 94<br>94<br>95 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.3 Configuring the Interface Between the Microprocessor<br>and the Support Chips                                                                                      | 99             |

|                                                                                                                                                                        | 99<br>102      |

|                                                                                                                                                                        | 102            |

| 2.3.2 Additional Address Assignment Techniques                                                                                                                         | 102            |

| 2.3.3 Interrupts                                                                                                                                                       | 104            |

|                                                                                                                                                                        | 106            |

|                                                                                                                                                                        |                |

| 2.3.3.3 Example 2: Using the Processor Software Power .                                                                                                                | 108            |

| 2.3.4 The Application of RDY to Controlling the Mem-                                                                                                                   |                |

| ory Interface                                                                                                                                                          | 108            |

| 2.3.4.1 Interface Slow PROMs                                                                                                                                           | 108            |

| 2.3.4.2 Direct Memory Address (DMA) Techniques                                                                                                                         | 112            |

|                                                                                                                                                                        | 113            |

| 2.3.5 Hold-Time ControlMCS6501                                                                                                                                         | 117            |

|                                                                                                                                                                        |                |

| 2.4 Additional System Considerations                                                                                                                                   | 119            |

| 2.4.1 Peripheral Interface Devices                                                                                                                                     | 119            |

| 2.4.2 RAM                                                                                                                                                              |                |

| 2.4.3 ROM                                                                                                                                                              |                |

| 2.5 Evaluating System Performance                                                                                                                                      | 121            |

## CHAPTER 3 BRINGING UP THE MCS6500

| 3.0 Introduction to Microcomputer Testing                                              |

|----------------------------------------------------------------------------------------|

| 3.1 Static Testing                                                                     |

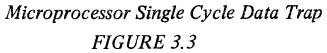

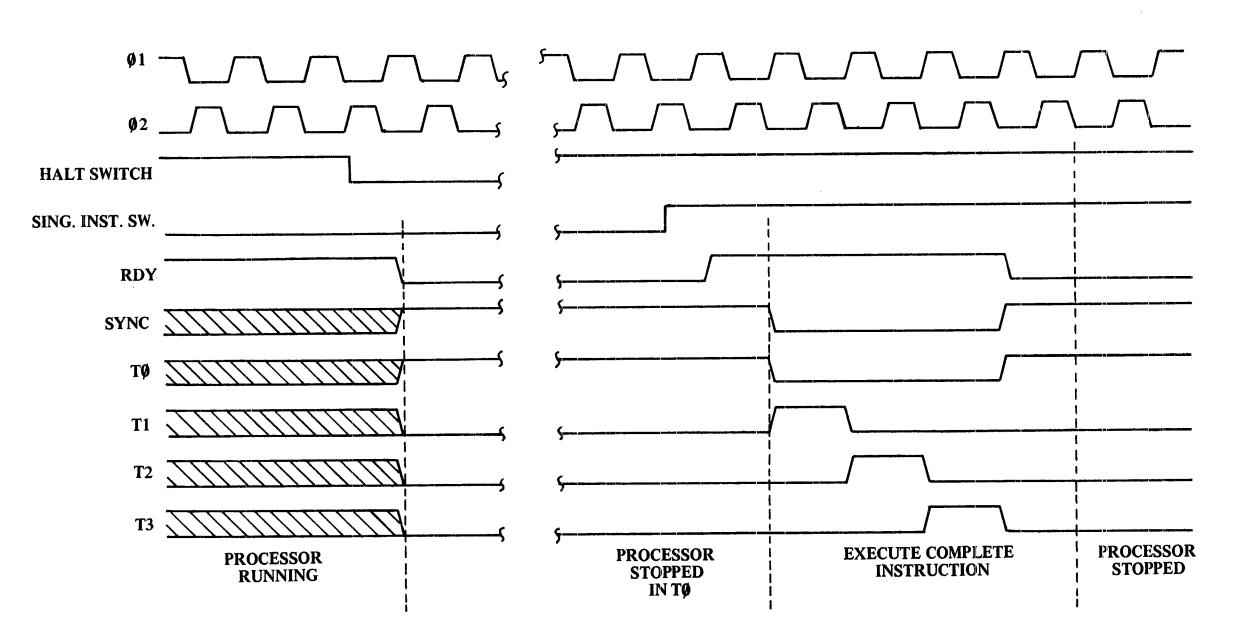

| 3.1.1Introduction1243.1.2Single Cycle Execution1243.1.3Single Instruction Execution127 |

| 3.2 Dynamic Testing                                                                    |

| 3.2.1 Introduction 130   3.2.2 Externally Induced Loops 130   3.2.3 Software Loops 132 |

3.3 System Diagnosis Using Hardware Programmer Aids. . . 133 3.3.1 3.3.2 3.3.3 MDT--Microcomputer Development Terminal. . . . . 138 3.4.1 3.4.2 3.4.3 3.4.4

. ..

| APPENDIX A . | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | A– | 1 |

|--------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|---|

|              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |   |

# **LIST OF FIGURES**

## CHAPTER 1 THE MCS6500 MICROCOMPUTER SYSTEM

| 1.1   | Organization of Microcomputer System                       |    |

|-------|------------------------------------------------------------|----|

| 1.2   | Address Bus and Relation to Memory Field                   | 7  |

| 1.3   | Portion of Read Only Memory Matrix                         | 9  |

| 1.4   | Pinout Comparison: MOS Technology MCS6501, Motorola MC6800 |    |

| 1.5   | Clock and Read/Write Timing Table (1 MHz Operation)        | 17 |

| 1.6   | Two-Phase Clock Timing.                                    |    |

| 1.7   | Timing for Reading Data from Memory of Peripherals         | 18 |

| 1.8   | Timing for Writing Data to Memory or Peripherals           | 19 |

| 1.9   | Interrupt Wire OR'd Hardware Configuration from Peripheral |    |

|       | Interface Devices to Microprocessor                        | 24 |

| 1.10  | Sequence to Service IRQ                                    |    |

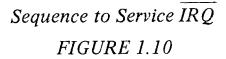

| 1.11  | MCS650X Internal Architecture                              |    |

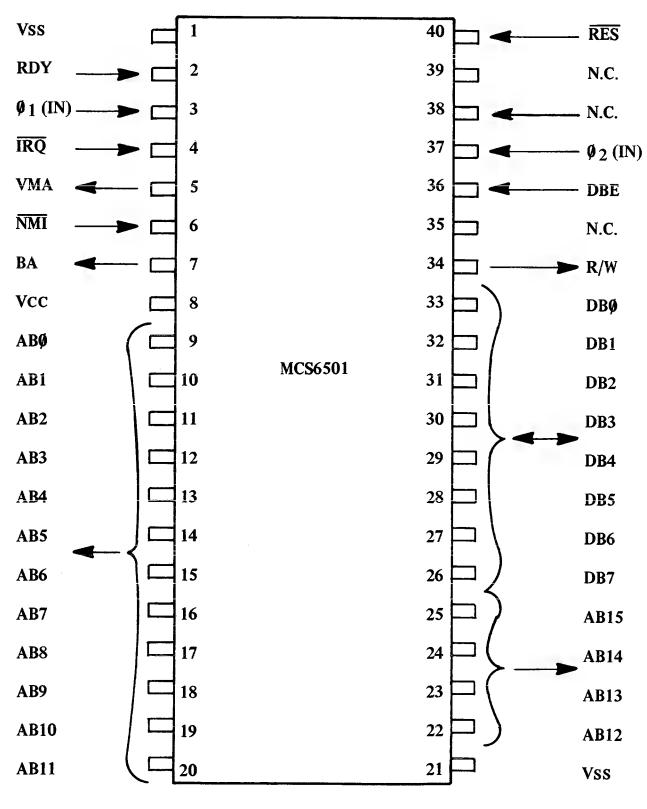

| 1.12  | MCS6501 Pinout Designations                                |    |

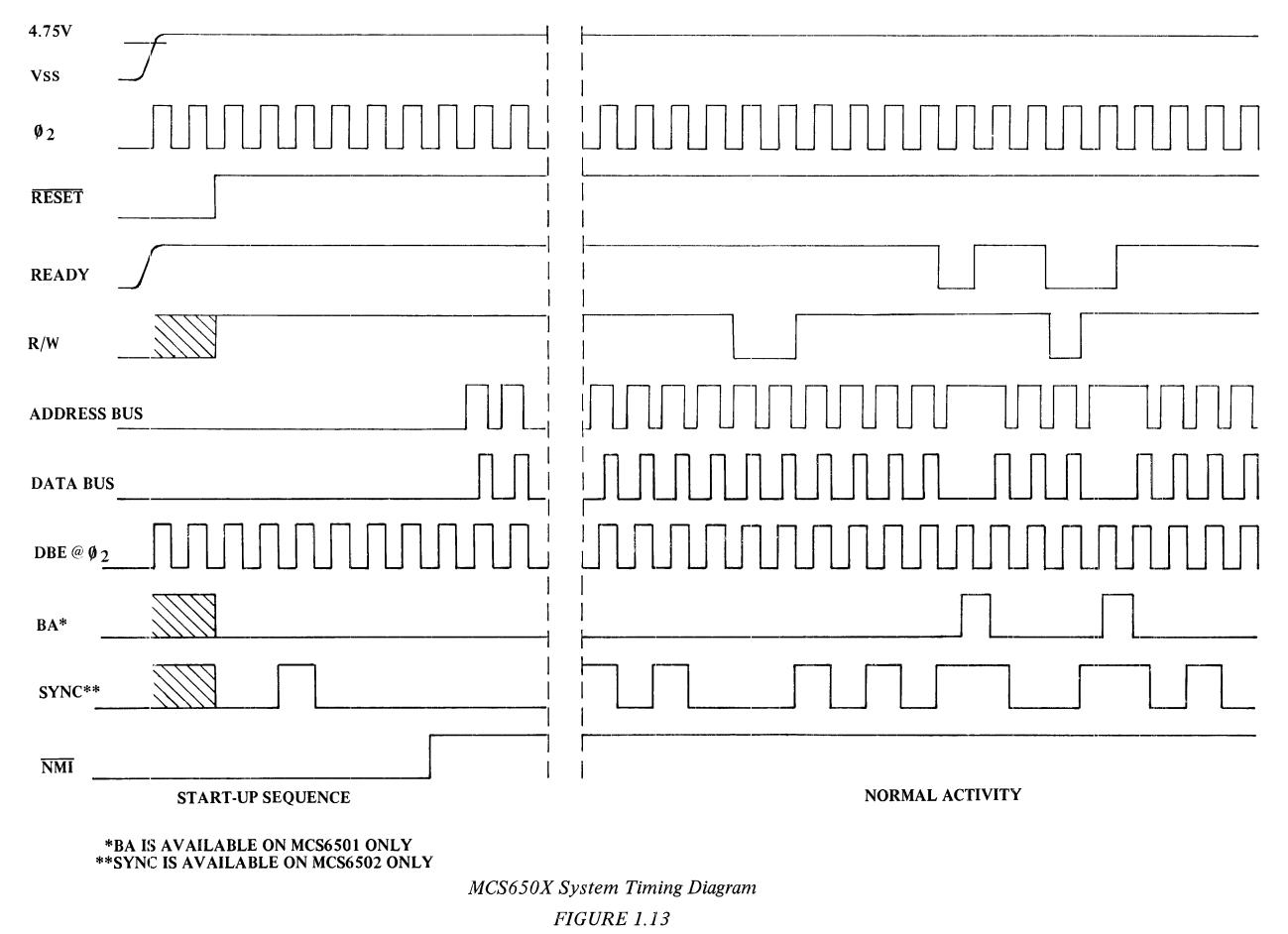

| 1.13  | MCS650X System Timing Diagram                              |    |

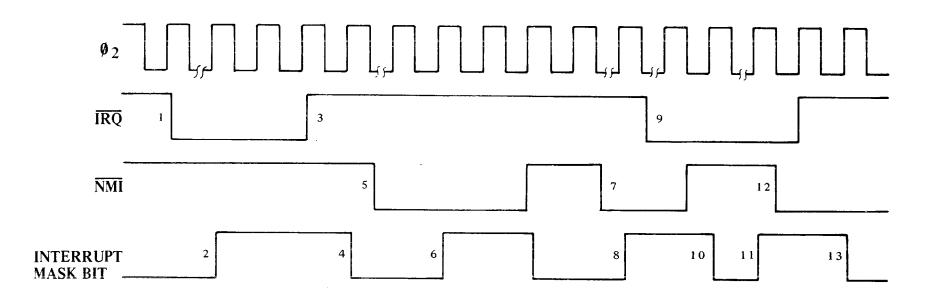

| 1.14  | Examples of Interrupt Recognition by MCS650X               |    |

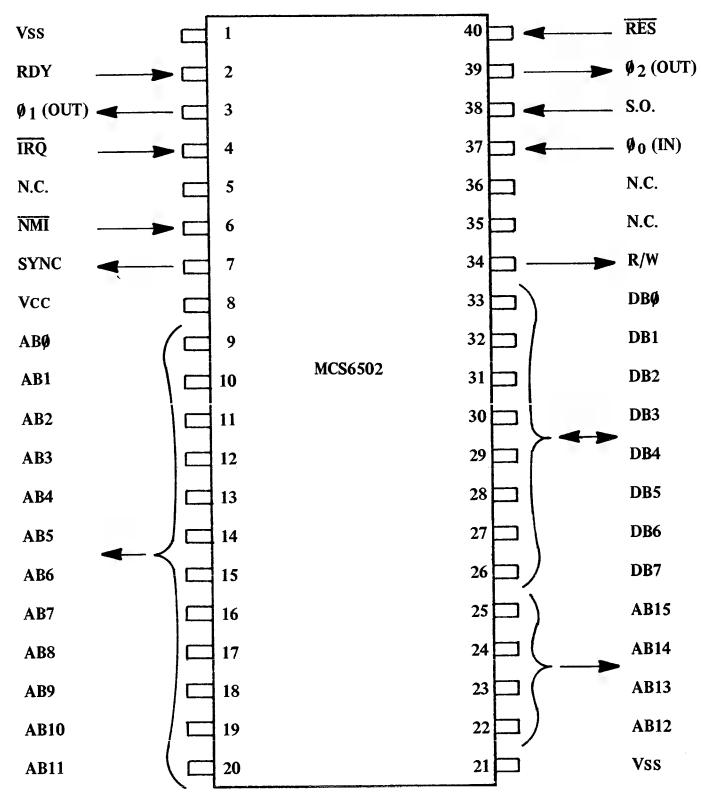

| 1.15  | MCS6502 Pinout Designation                                 |    |

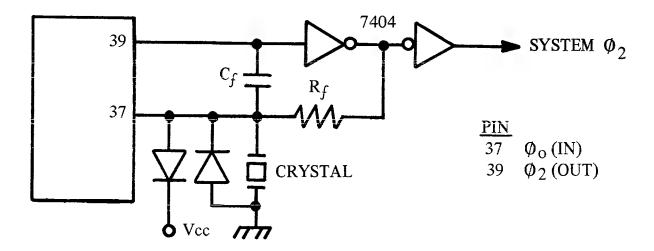

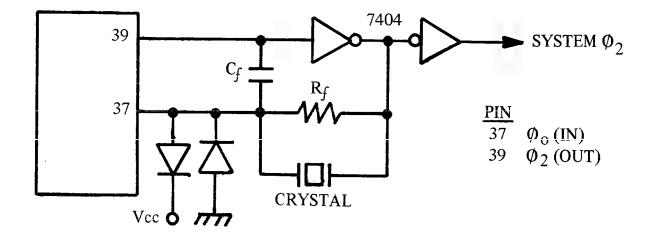

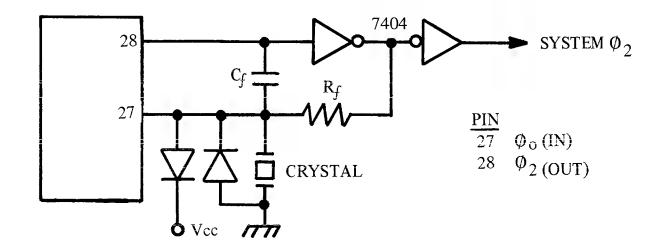

| 1.16  | MCS6502 Time Base GenerationCrystal Controlled             |    |

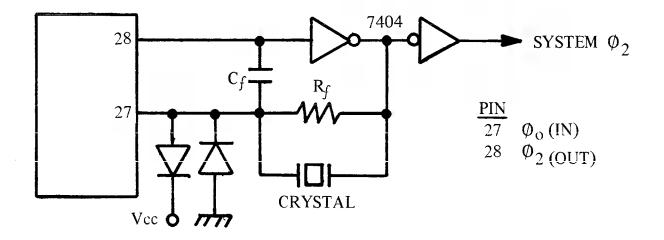

| 1.16a | MCS6502 Parallel Mode Crystal Controlled Oscillator        |    |

| 1.16b | MCS6502 Series Mode Crystal Controlled Oscillator          |    |

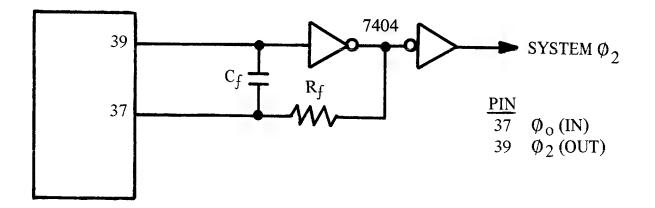

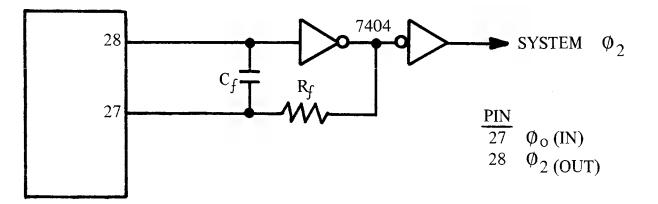

| 1.17  | MCS6502 Time Base GeneratorRC Network                      |    |

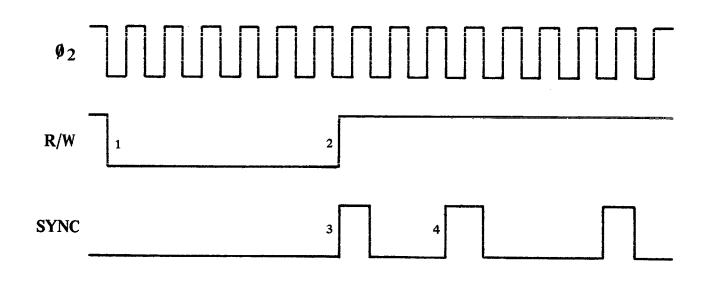

| 1.18  | MCS6502 SYNC Signal                                        |    |

| 1.19  | Functional Features of MCS6503, MCS6504, MCS6505           |    |

| 1.20  | MCS6503, MCS6504, MCS6505 Pinout Designations              |    |

| 1.21  | MCS6503, MCS6504, MCS6505 Time Base Generation Crystal     |    |

|       | Controlled                                                 | 49 |

| 1.22  | MCS6503, MCS6504, MCS6505 Time Base Generation RC Network  |    |

| 1.23  | Basic MCS6520 Interface Diagram                            |    |

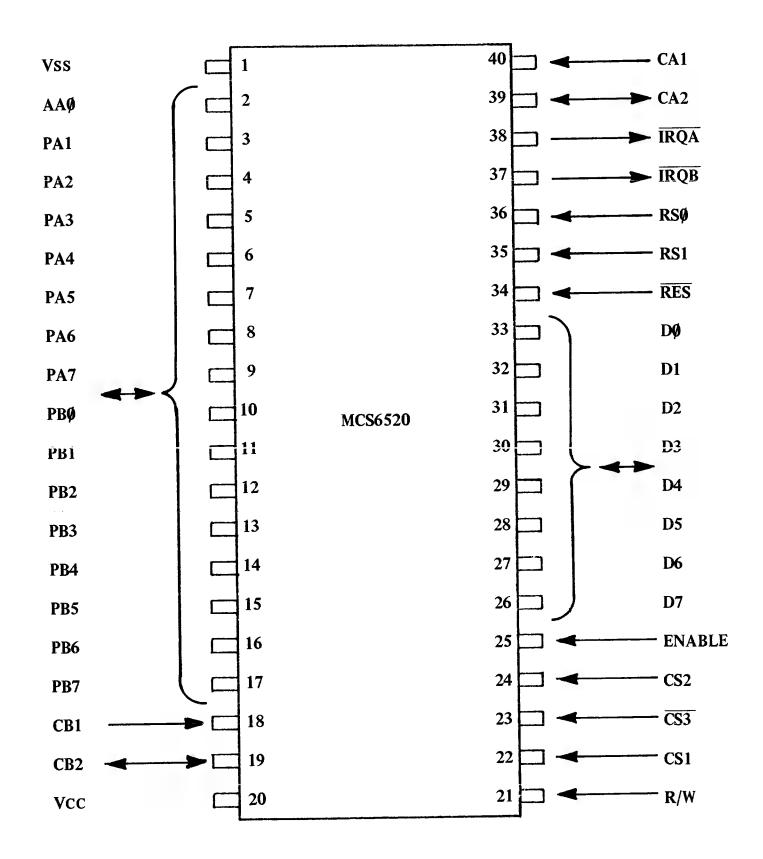

| 1.24  | MCS6520 Pinout Designations Peripheral Interface Adaptor   |    |

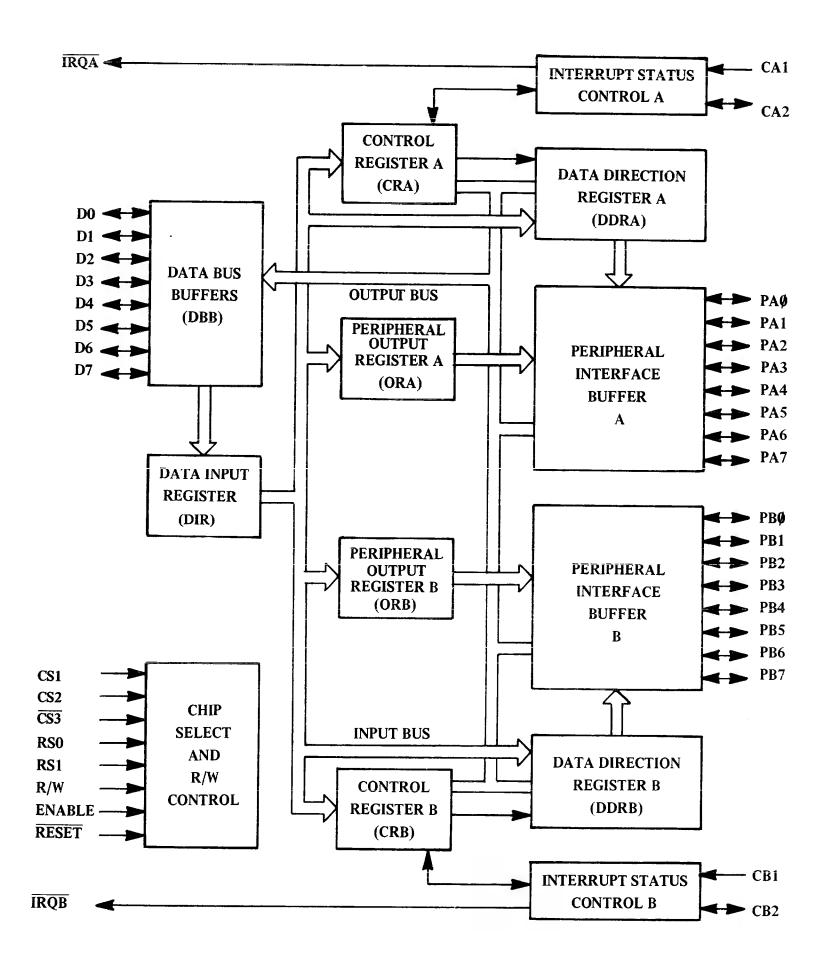

| 1.25  | MCS6520 Internal Architecture                              |    |

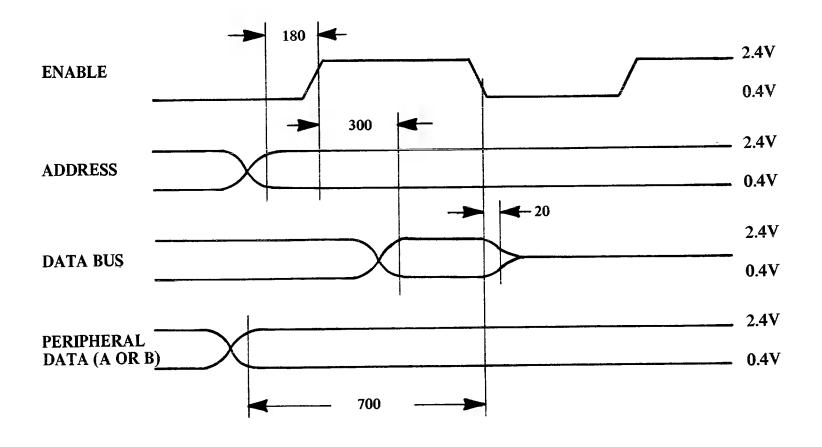

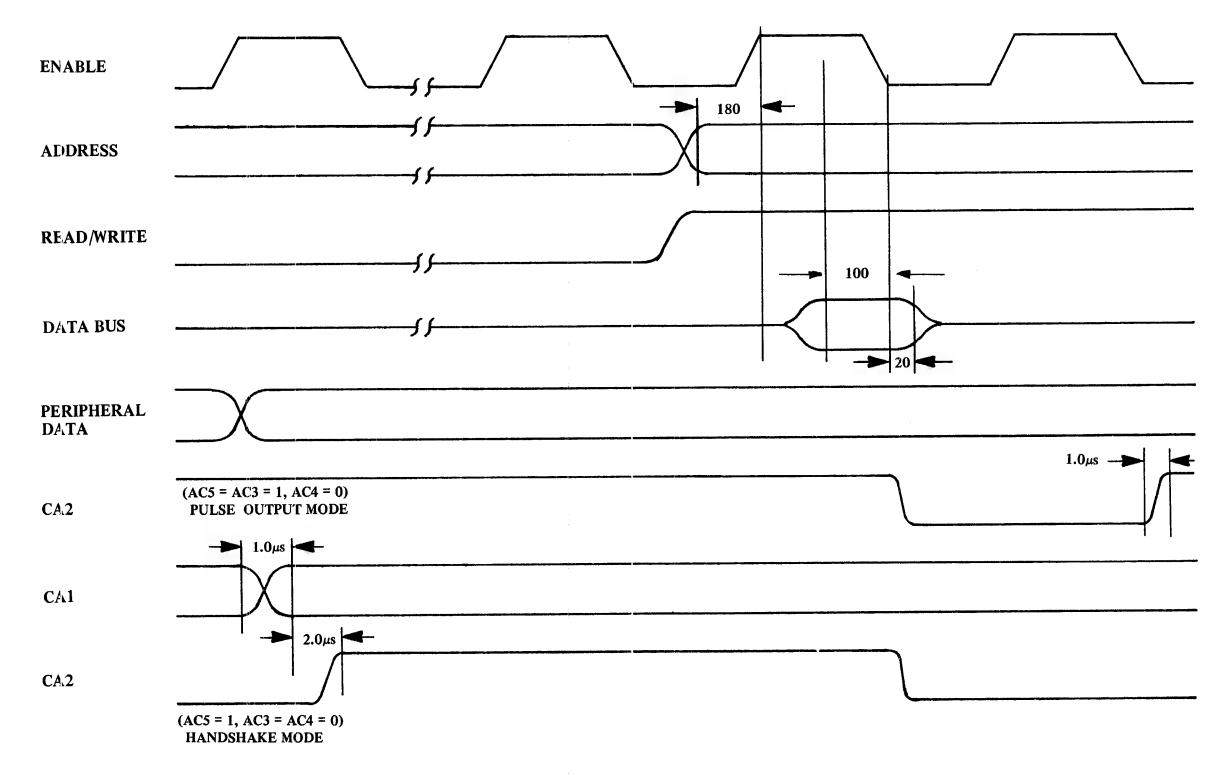

| 1.26a | Microprocessor Interface TimingRead                        |    |

| 1.26b | Microprocessor Interface TimingWrite                       |    |

| 1.27a | Peripheral A Interface Timing                              |    |

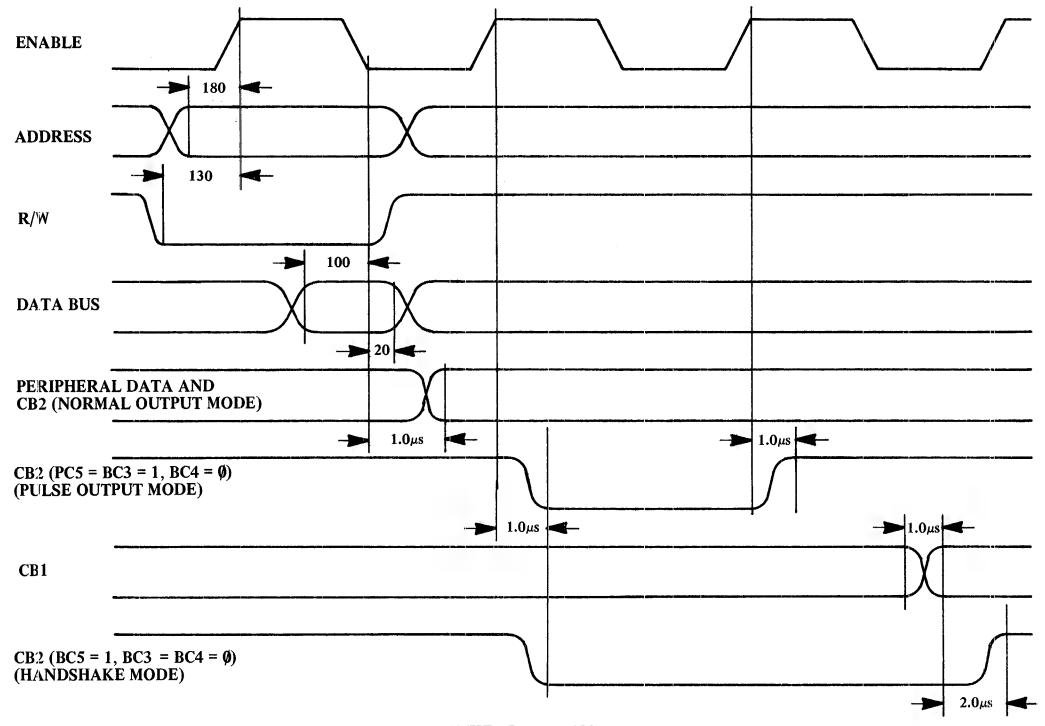

| 1.27b | Peripheral B Interface Timing                              |    |

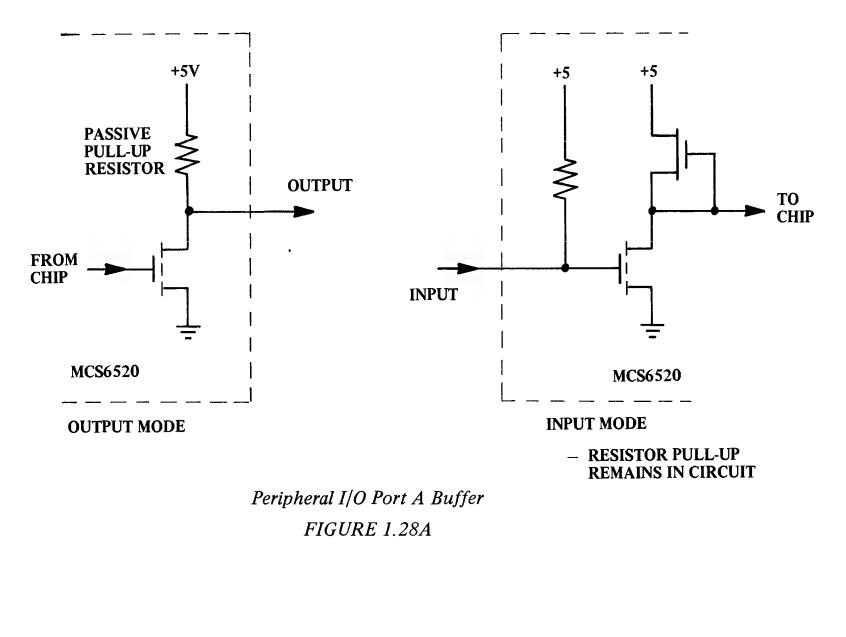

| 1.28a | Peripheral I/O Port A Buffer.                              |    |

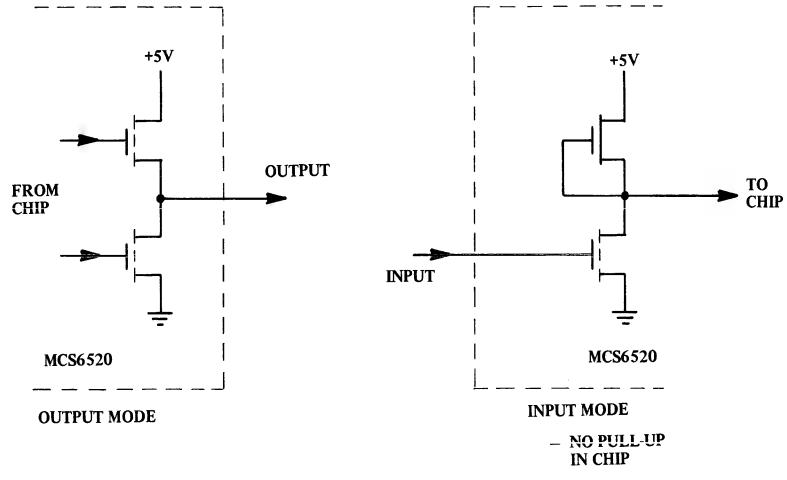

| 1.28b | Peripheral I/O Port B Buffer.                              |    |

| 1.200 | Control Register Bit Designations                          |    |

| 1.647 | concret westerer pre peersustrous                          | 07 |

| 1.30  | Control of Interrupt Inputs CA1, CB1                    | • | • | • | • | 68 |

|-------|---------------------------------------------------------|---|---|---|---|----|

| 1.31a | Control of CA2 (CB2) as Interrupt Inputs (Bit 5 = "0"). | • | • | • | • | 68 |

| 1.31b | Control of CA2 Output Modes                             | • | • | • | • | 69 |

| 1.31c | Control of CB2 Output Modes                             | • | • | • | • | 69 |

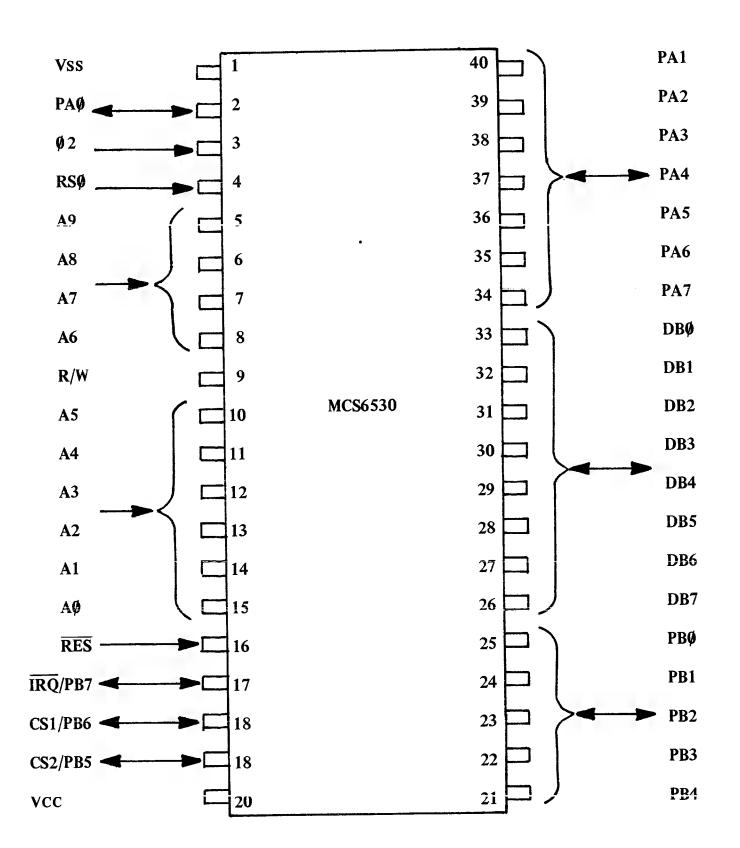

| 1.32  | MCS6530 Pinout Designation                              | • | • | • | • | 72 |

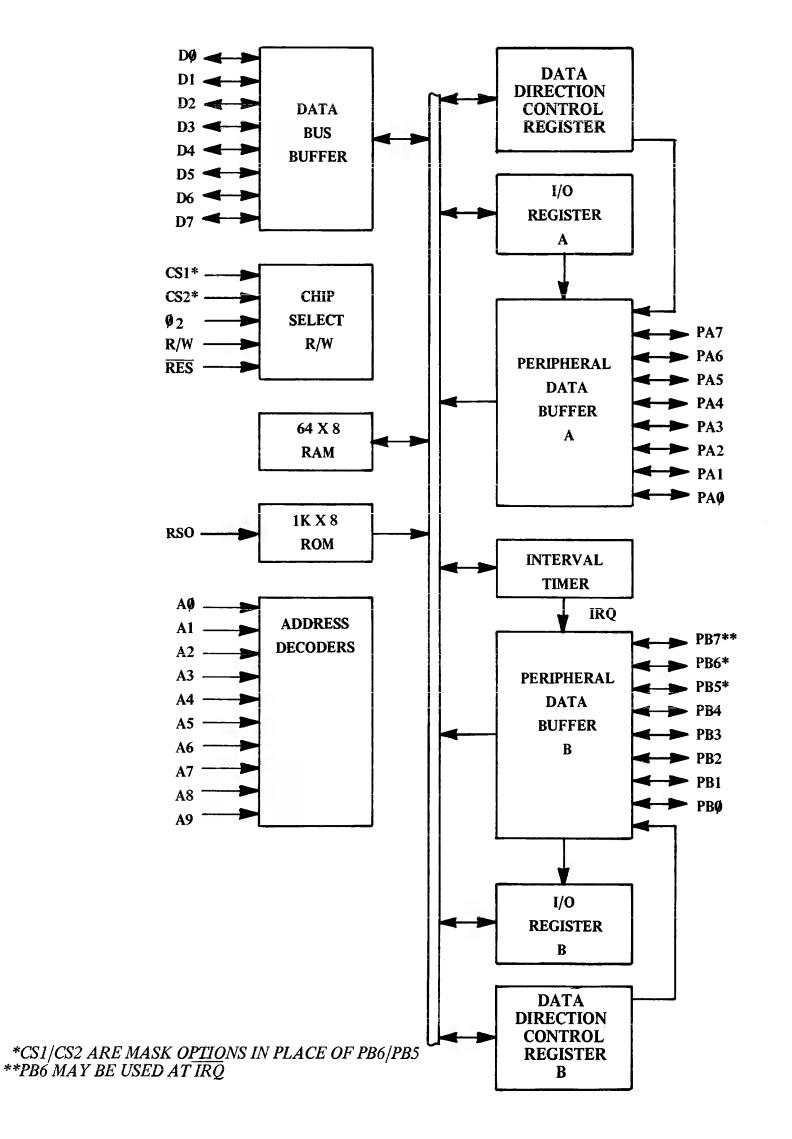

| 1.33  | MCS6530 Internal Architecture                           | • | • | • | • | 75 |

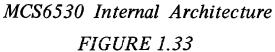

| 1.34  | Basic Elements of Interval Timer                        | • | • | • | • | 77 |

| 1.35  | Example of Interrupt Generated by Interval Timer        | • | • | • | • | 79 |

| 1.36  | MCS6530 One-Chip Address Encoding Diagram               | • | • | • | • | 81 |

| 1.37  | MCS6530 Seven-Chip Addressing Scheme                    | • | • | • | • | 82 |

| 1.38  | Addressing Decode for I/O Register and Timer            | • | ٠ | • | • | 83 |

.

## CHAPTER 2 CONFIGURING THE MICROCOMPUTER SYSTEM

| 2.1 Control of Low Order Bit of MCS6520 Output Register          | 89    |

|------------------------------------------------------------------|-------|

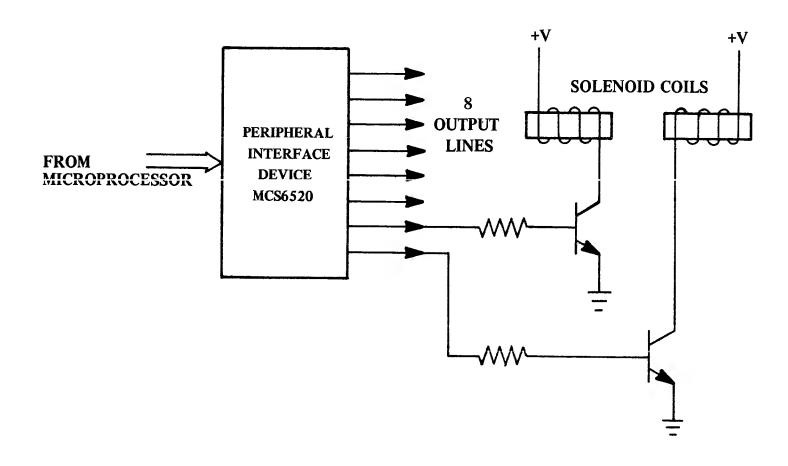

| 2.2 MCS6520 Control of Transistor Driven Solenoids               | 91    |

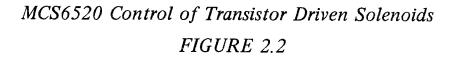

| 2.3a MCS6520 Control of PNP Transistor Driving Solenoid Coil     | 93    |

| 2.3b MCS6520 Controlling Both Power and Drivers of Solenoid Cell | . 93  |

| 2.4 MCS6520 Driving TTL Buffers                                  | 93    |

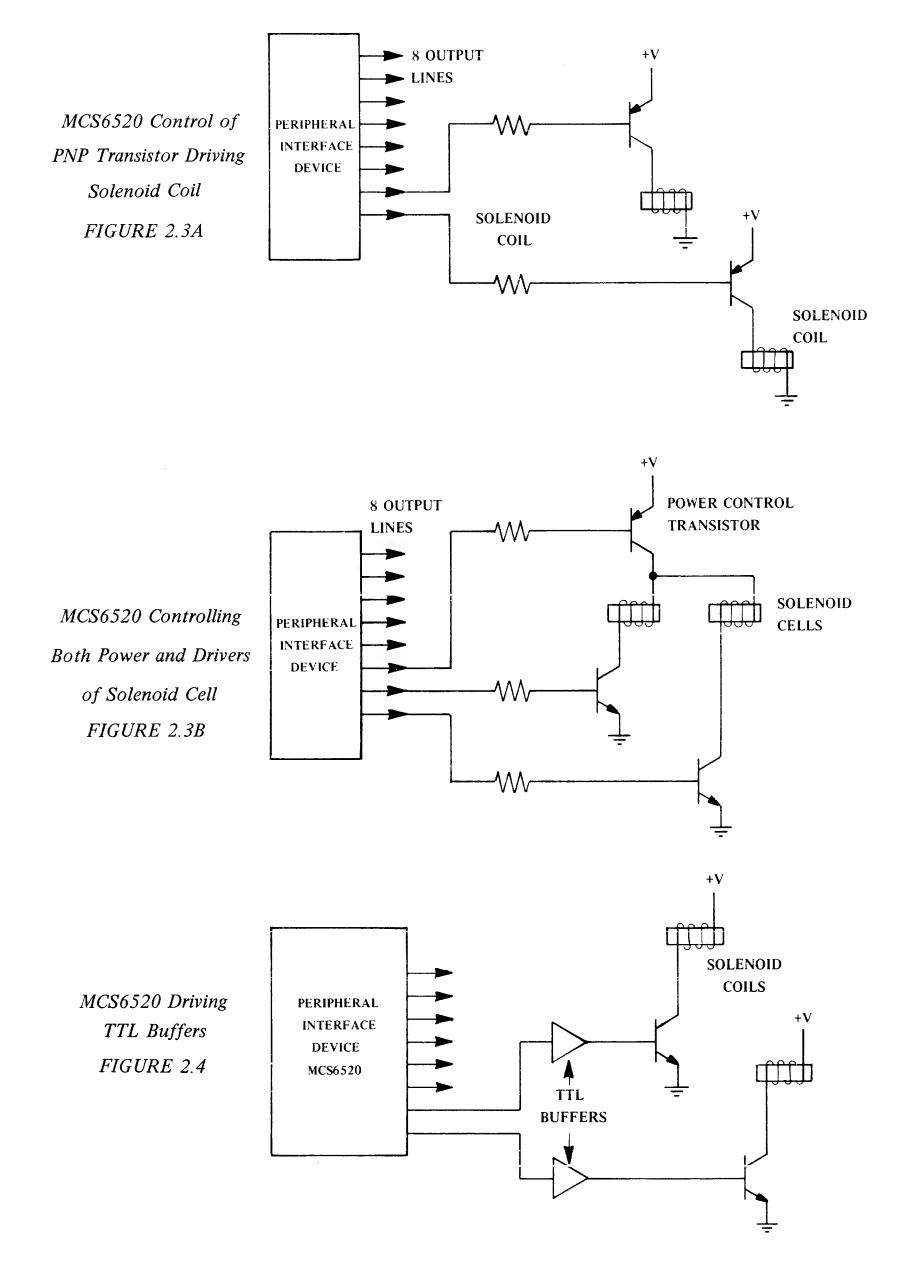

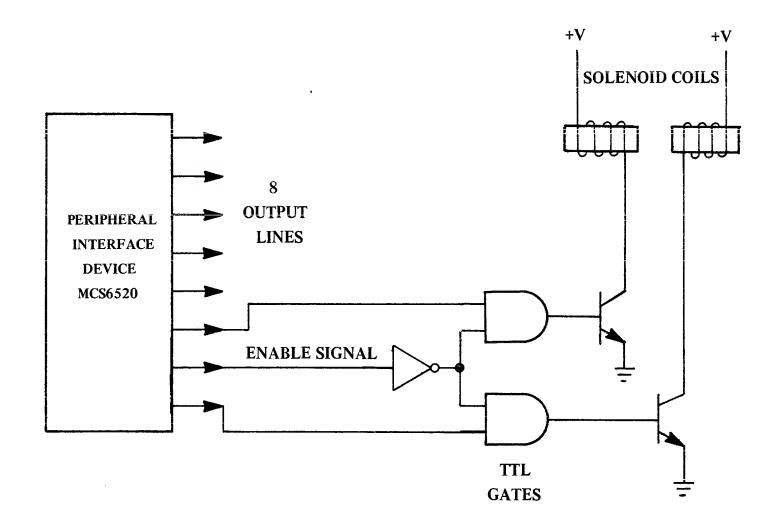

| 2.5 MCS6520 Controlling Solenoids with Enable Signal and TTL     |       |

| Interface                                                        | . 94  |

| 2.6 Write Handshake Sequence                                     | 97    |

| 2.7 Read Handshake Sequence                                      | . 98  |

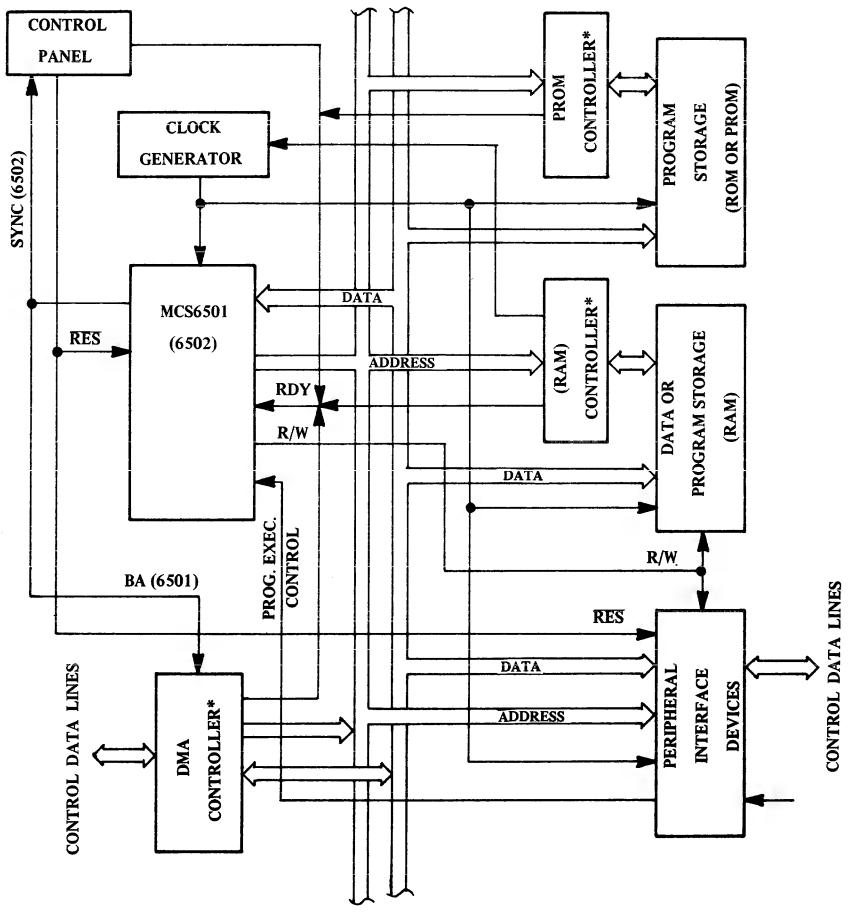

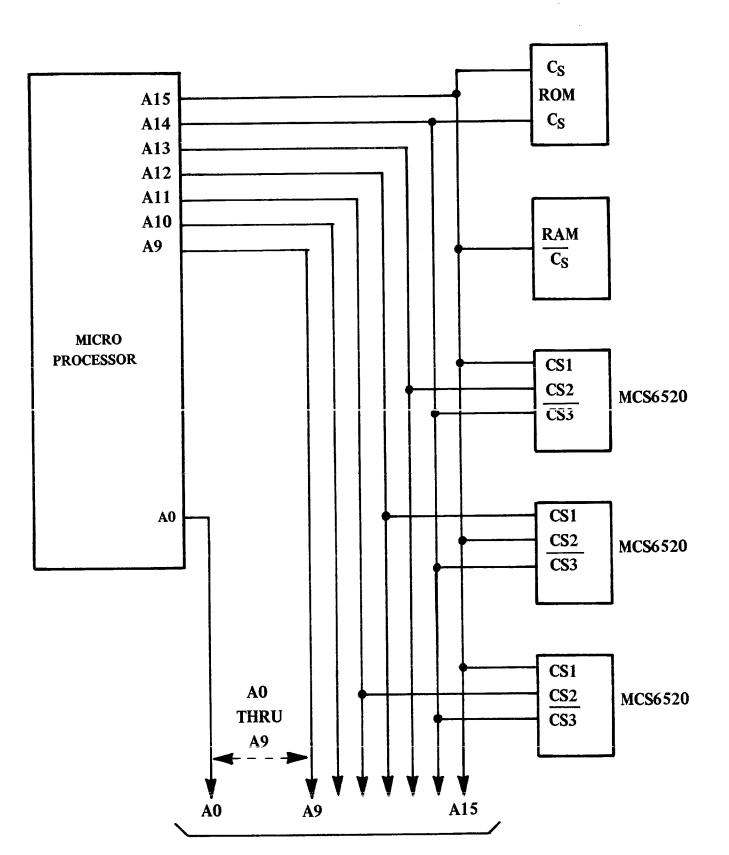

| 2.8 Organization of Microcomputer System                         | . 100 |

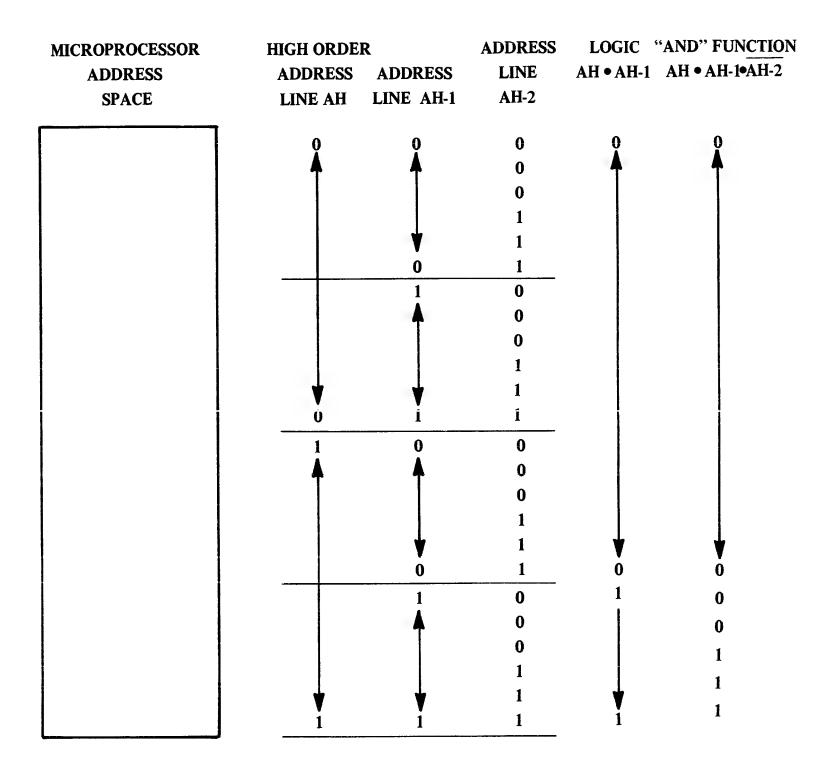

| 2.9 Example of "AND" Function Using High Order Address Lines     | . 101 |

| 2.10 Typical Address Assignments                                 | . 103 |

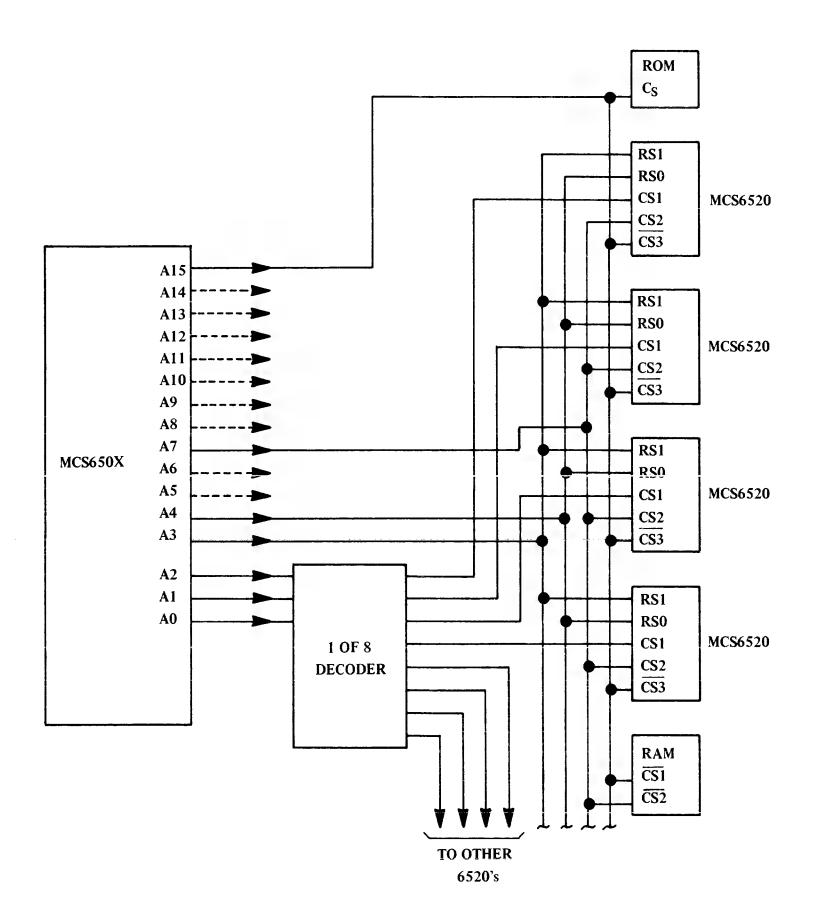

| 2.11 Page Zero Chip-Select Addressing Scheme                     | . 105 |

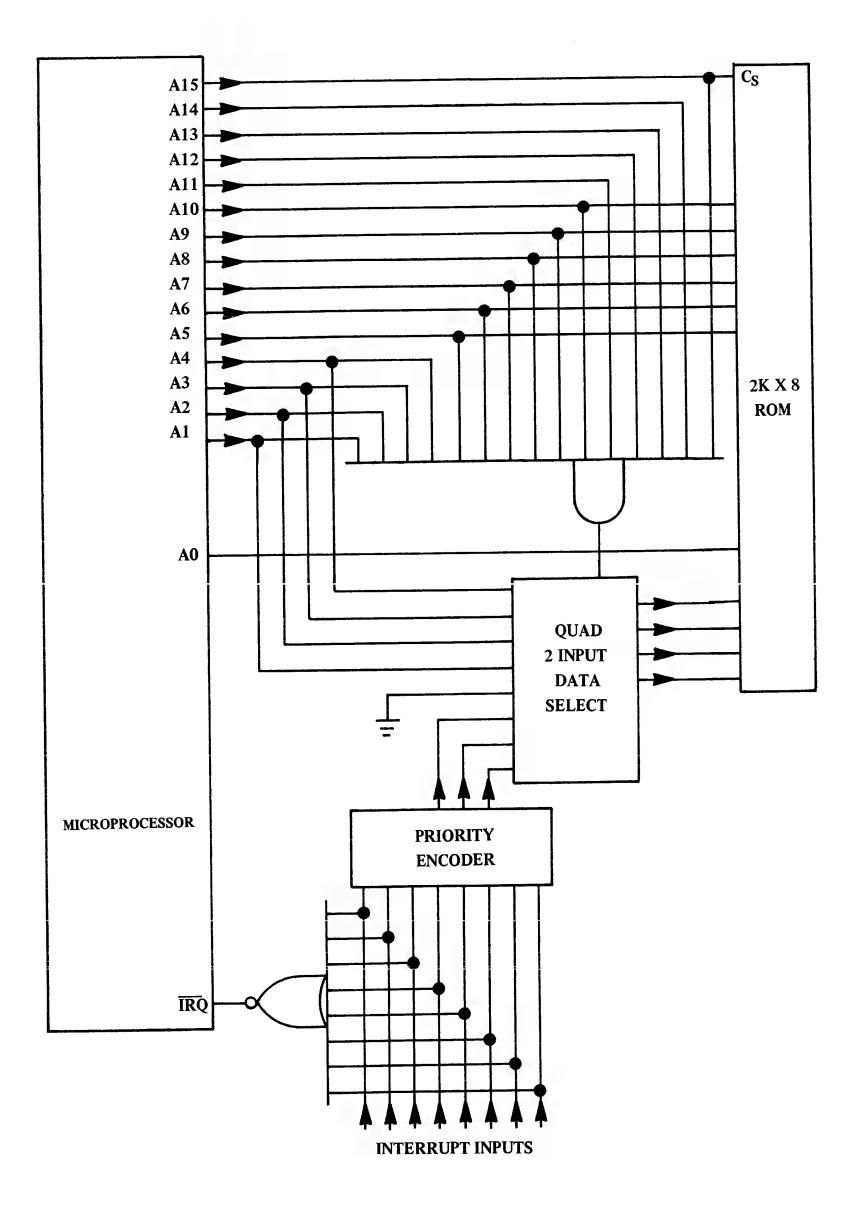

| 2.12 Selecting the Interrupt Vector                              | . 107 |

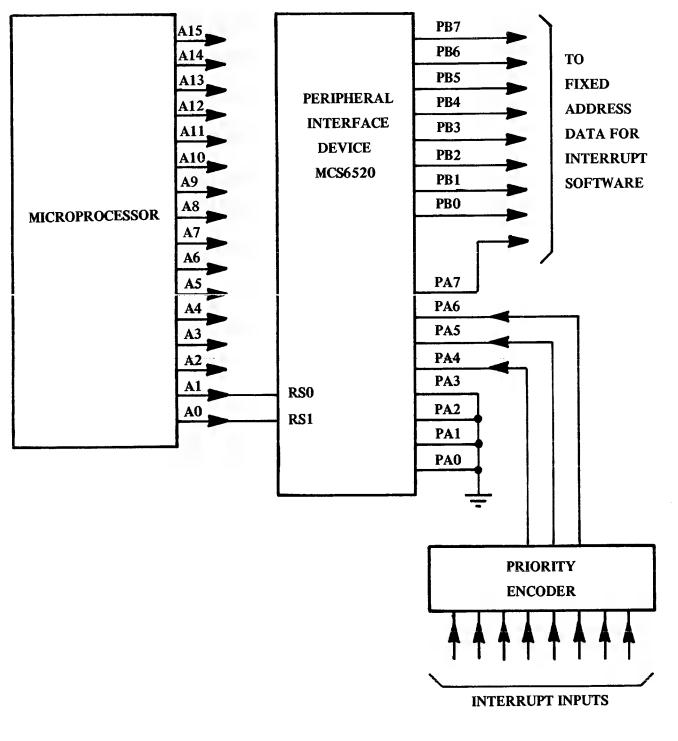

| 2.13 Using MCS6520 for Jump Indirect Interrupt Routines          | . 109 |

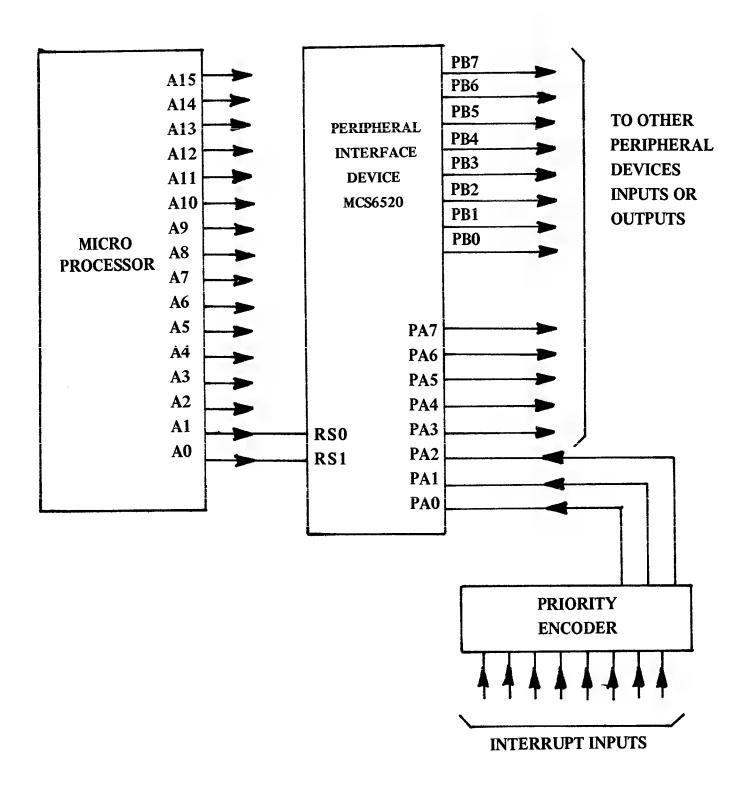

| 2.14a Priority Encoder Connected to Low Order Bits of MCS6520    | . 110 |

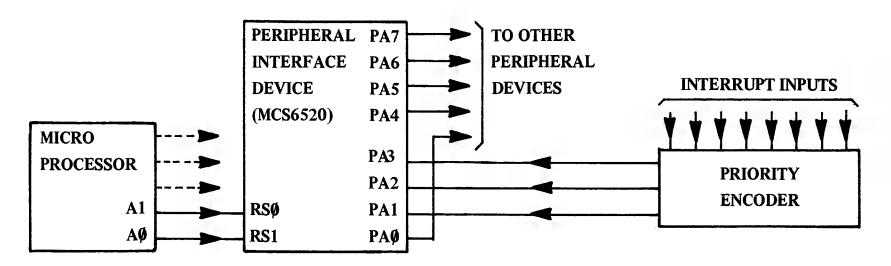

| 2.14b Priority Encoder to Peripheral Interface Scheme            | . 111 |

| 2.15 Software Program to Implement Interrupt from above Hardware |       |

| Configuration                                                    | . 111 |

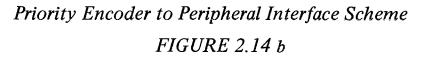

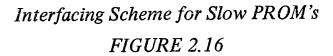

| 2.16 Interfacing Scheme for Slow PROMs                           | . 114 |

| 2.17 Logic Used to Generate Bus Available Signal for DMA         |       |

| Applications                                                     | . 114 |

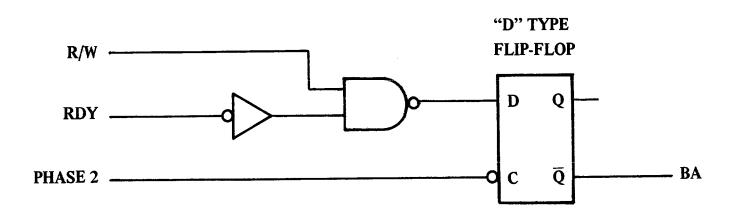

| 2.18 Control Logic for Refresh Signal for Dynamic RAMs           | . 116 |

|                                                                  | • 110 |

## CHAPTER 3 BRINGING UP THE MCS6500

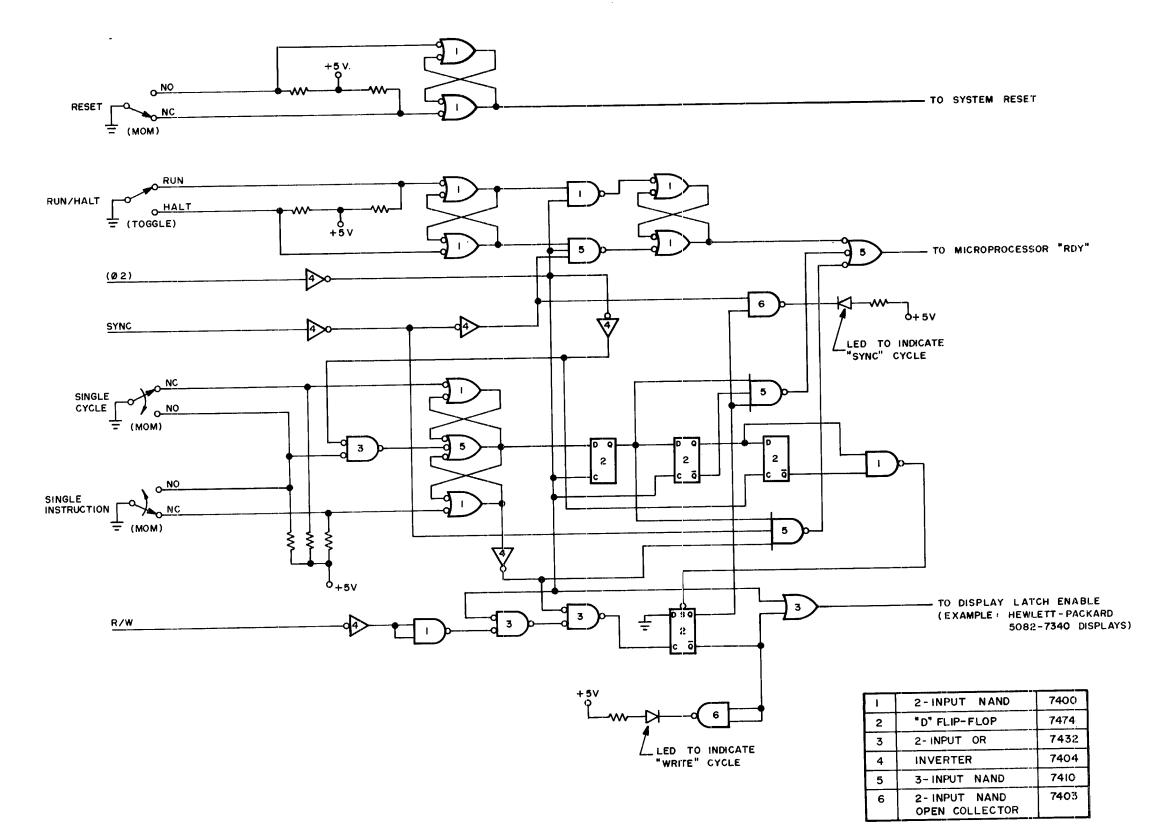

| 3.1  | Suggested Static Test Control Logic                   |

|------|-------------------------------------------------------|

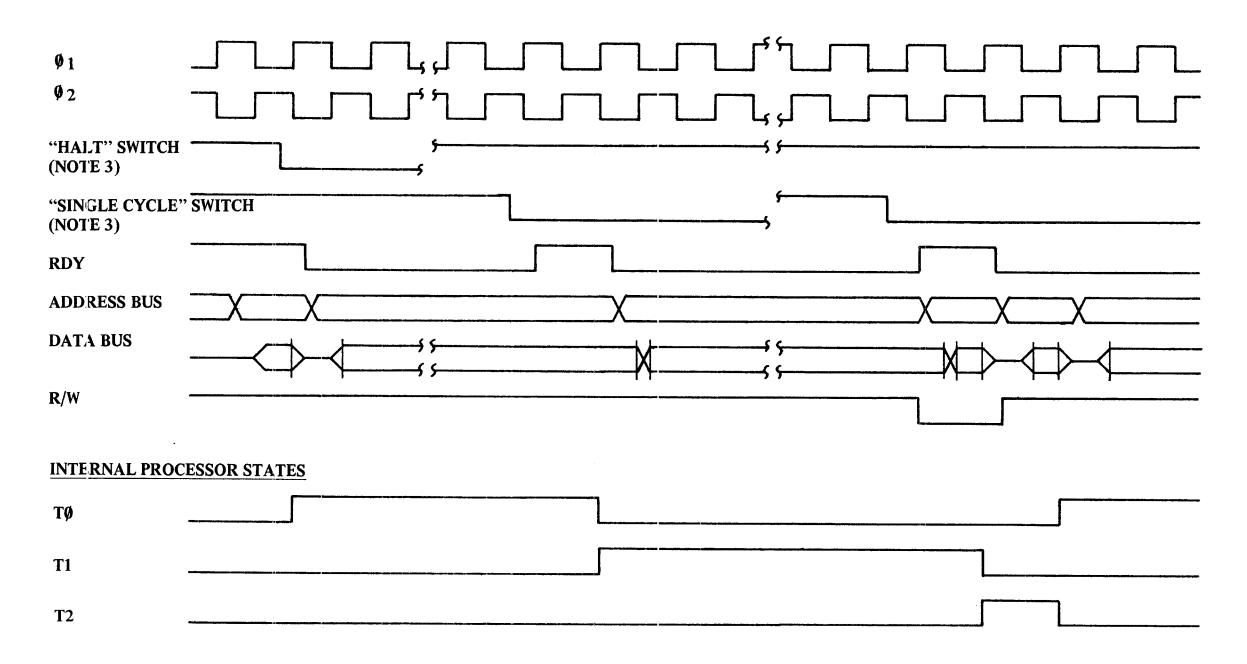

| 3.2  | Single Cycle Timing                                   |

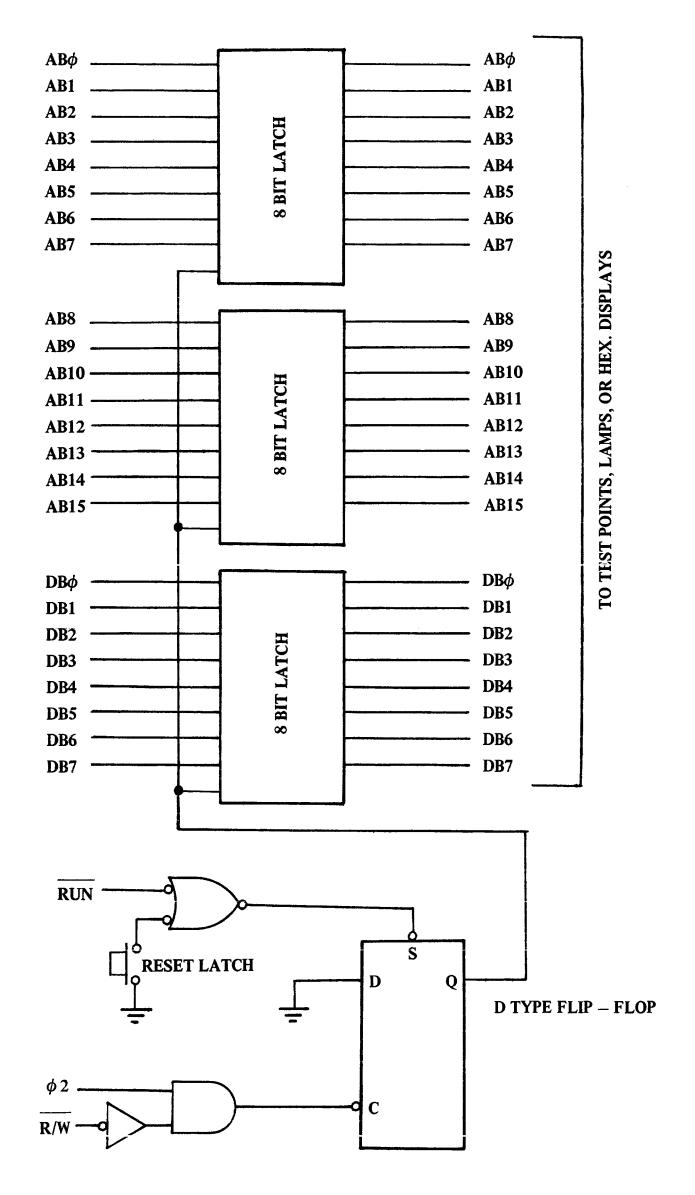

| 3.3  | Microprocessor Single Cycle Data Trap                 |

| 3.4  | Single Instruction Execution                          |

| 3.5  | Suggested Configuration for Dynamic Reset Testing 131 |

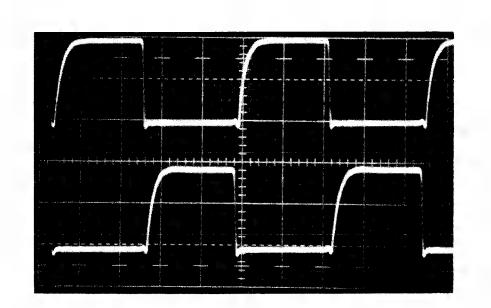

| 3.6  | MCS6501 Clock Timing Signals                          |

| 3.6a | Improper Clocks                                       |

| 3.6b | Proper Clocks                                         |

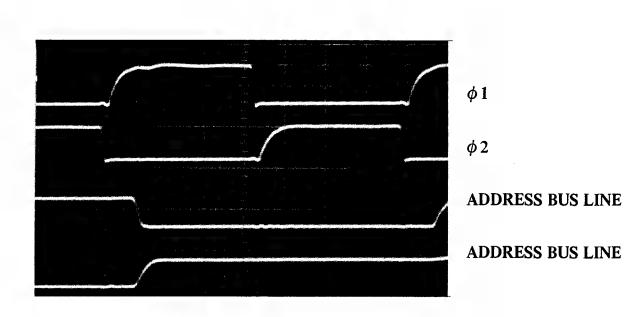

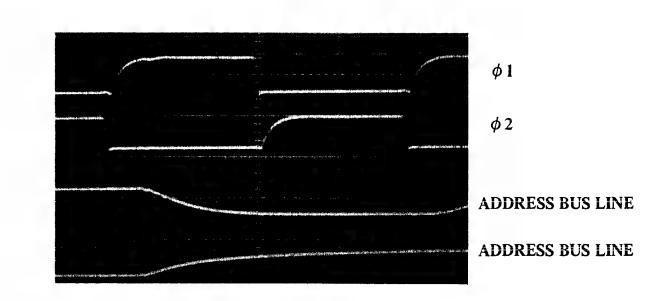

| 3.7  | Address Lines in MCS650X Systems                      |

| 3.7a | Proper Address Lines                                  |

| 3.7Ъ | Excess Address Line Loading                           |

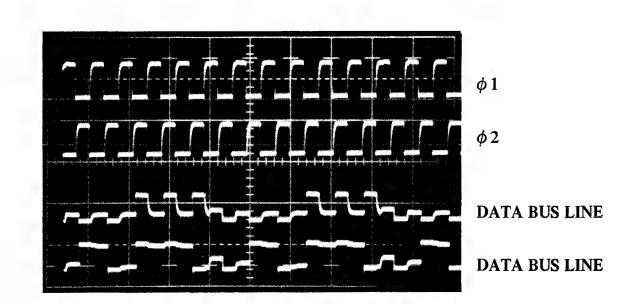

| 3.8  | The Data Bus in MCS650X Systems                       |

#### CHAPTER 1

#### THE MCS6500 MICROCOMPUTER SYSTEM

The past several years have seen the development of an exciting new concept in electrical design. Conventional system design is rapidly being revolutionized by the large-scale, single-chip programmable microprocessor. The microcomputer started out as a relatively simple, difficult-to-use programmable device capable of handling simple control or computational problems. However, it has since matured into a powerful, inexpensive, easy-to-use device capable of controlling all but the most complex of systems.

Three primary attributes of microprocessor-based systems are bringing about this revolution. They are:

- Microprocessors allow a significant reduction in overall systems cost for products currently in production. Re-designing their products around the microprocessor is permitting many manufacturers to develop or maintain a price advantage over competitors.

- 2. The reduction in cost of microcomputer systems is opening up vast new markets for microprocessors. A great number of systems which were simply impossible or were at best impractical, are being designed and marketed today using the modern, low-cost microprocessors.

- 3. At the same time the price of microprocessors is dropping, the capability is rapidly expanding. This also allows them to be designed into more systems than ever before.

Anyone contemplating a new design or trying to reduce cost in an existing design must ask himself if a microprocessor will solve his problem.

The success of the microprocessor is based on the fact that it allows the design engineer and programmer to apply their expertise in solving a multitude of design problems using cost effective ICs. A small number of large integrated circuits can be configured to solve design problems from the simplest to the most complex.

-1-

If the same integrated circuits are used to solve a multitude of unique designs, the first question one must ask is, "What makes them unique?" The answer is: <u>Programming</u>. Although many different designs may share common hardware, each has its own unique program. This brings us to another very important characteristic of microcomputers. The integrated circuit which makes each system unique is the "Read-Only Memory" (ROM) which stores the system program. It is relatively easy for the integrated circuit manufacturer to establish the particular pattern which uniquely defines the data in a ROM. As a result, the typical charge for "designing" a ROM is generally less than 10% of the cost of designing a totally custom logic chip. Further, the user benefits from high volume standard product which is still unique for his own application due to the "customization" of one element of his system.

#### 1.0 DESIGNING WITH MICROCOMPUTER SYSTEMS

It will probably surprise many designers who are approaching the subject of microcomputer design for the first time when they discover that designing a system around a microprocessor is much the same as designing around conventional logic. The total approach is the same; the process differs only in the implementation of each step.

A brief examination of the system design process will help to put microcomputer design in perspective and will also assist in clarifying the purpose of this manual. One can expect to perform the following steps in designing a system:

- 1. Define the requirements of the system. What functions should it perform?

- 2. Define basic system components.

- 3. Complete design details.

- 4. Build and test prototypes.

- 5. Finalize design and begin production.

Step 1 is true for any system and, in general, for any product. Step 2 is the first point of departure for microprocessor based designs. It is at this time that the designer must consider the possibility of using a microprocessor in his system. For the very cost-sensitive application he must look very carefully at total systems cost. Can a microprocessor do the job within the price constraints imposed? At the other end of the design spectrum, the system designer must evaluate the capability of microprocessors to assure himself that the available devices can in fact perform the required function. Will a microprocessor be fast enough to run the system? Will it take more than one processor?

The purpose of this manual is to teach the designer how to effectively configure a microprocessor-based system and to evaluate the performance of the system. After this step, the design will be completed by development of the system program. Implementation of the system program is discussed in the Programming Manual.

-3-

#### 1.1 INTRODUCTION TO MICROCOMPUTER SYSTEMS

#### 1.1.1 Organization of a Microcomputer System

Figure 1.1 illustrates the basic organization of a microcomputer system. It is important that the designer understand the operation of each component as well as the operation of each data path in the system. Each of these is discussed separately below. In addition, the following discussion describes the operation of the overall system and the use of the various signal paths.

#### 1.1.2 Basic Operation

The microcomputer is a system which can be characterized as very simple in its detail and very complex in its overall operation. It carries out rather complex tasks by performing a large number of simple operations. Control of the system is primarily the responsibility of the processor. By putting out addresses to program memory, it controls the sequence of operations performed and by interpreting and executing the instructions which it receives from the program memory, it controls the actual operations carried out by the system. The processor is by far the most complex device in the system. For this reason, it is important to overall system cost that this part stay the same for many different applications. In this way, the relatively high development cost can be shared by thousands of users. In addition, those thousands of users can all benefit from the economics of large-scale production.

The processor causes the system to perform the desired operations by reading the first instruction in the program, and performing the very simple task dictated by the specific pattern of bits in this instruction (referred to as "executing" that instruction). It then goes on to the next instruction in the program and executes it. This simple operation of fetching an instruction and executing it is performed over and over, each time on the next instruction in sequence. In this way the program instructs the processor to bring about the desired system operation.

#### 1.1.3 Addressing Terms and Concepts

Before entering into a detailed discussion of the system operation, it would be useful to define a few terms and to introduce a few concepts concerning addressing. This should assist in an understanding of the detailed discussions which follow.

-4-

Organization of Microcomputer System FIGURE 1.1

#### 1.1.3.1 Bit

The term "Bit" is a general term referring to anything that can be assigned to binary value, i.e., anything that can be given a value of 0 or 1. Thus, an eight-bit data bus is a set of 8 lines which can be assigned a value of logic 0 or logic 1. On these lines, the logic values are represented by two different voltages or currents. Similarly, a 16-bit binary display can be built with 16 individual lamps. The logic 1 is represented by the lamp being on.

In this text, reference is made to an 8-bit data bus, a 16-bit address bus, 4 bits of data, 8-bit registers, etc. In all cases, definition of a bit remains the same.

#### 1.1.3.2 Address Space

The concept of an address space is very useful in understanding microcomputer systems. The term "address space" refers to the total set of addresses which the microprocessor can generate. For example, if a processor had only 4 address lines, it could generate the addresses 0 - 15 (binary 0000 to binary 1111). This would not be adequate for any microcomputer operation and, consequently, the typical processor has between 12 and 16 address lines. Since each line can assume a value of 0 or 1, these devices can usually address from 4,096 to 65,536 separate addresses. Figure 1.2 contains a pictorial representation of the address space available in a typical 8-bit microcomputer with sixteen address lines. In addition to the general address space, this figure introduces the PAGE concept discussed below.

#### 1.1.3.3 The Address Page

The concept of a PAGE in memory is very important in 8-bit microcomputer systems. The internal organization of an 8-bit processor is around 8-bit registers, 8-bit parallel data paths, etc. Most arithmetic operations, logic operations, etc. take place on 8 bits of data at a time. Likewise, the 16-bit counter which determines which instruction is being executed is actually divided into two 8-bit busses. One contains bits 0 - 7 (low order address bits) and the other contains bits 8 to 15 (high order address bits). With this in mind, one can think of the address space shown in Figure 1.2 as consisting of 256 blocks, each consisting of 256 specific address locations. Each of these blocks is referred to as a "PAGE"

-6-

| <u>BINARY ADDI</u><br><u>High Order</u> | RESS<br>Low Order | DECIMAL<br>WORD | HEXADECIMAL<br><u>Address Code</u><br>Page Byte | ADDRESSABLE<br>MEMORY FIELD   |

|-----------------------------------------|-------------------|-----------------|-------------------------------------------------|-------------------------------|

| 15 14 13 12 11 10 9 8                   | 7654 3210         | NUMBER          | Number Number                                   | (65536 Bytes)                 |

| 0 0 0 0 0 0 0 0                         | 0 0 0 0 0 0 0 0   | 0               | 00 – 00                                         |                               |

| 0 0 0 0 0 0 0 0                         |                   | 1               | 00 - 01                                         |                               |

| 0 0 0 0 0 0 0                           | 1111 1111         | 255             | 00 – FF                                         |                               |

| 0 0 0 0 0 0 0 1                         | 0000 0000         | 256             | 01 - 00                                         |                               |

|                                         |                   |                 |                                                 |                               |

| 1 1 1 1 1 1 1 0                         | ▼<br>1111 1111    | 65279           | FE – FF                                         |                               |

| 1 1 1 1 1 1 1 1                         | 0000 0000         | 65280           | FF - 00                                         |                               |

| 1 1 1 1 1 1 1 1                         |                   | 65281           | FF – 01                                         |                               |

| 1 1 1 1 1 1 1 1                         | 1111 1111         | 65535           | FF – FF                                         |                               |

|                                         |                   |                 |                                                 | D <sub>7</sub> D <sub>0</sub> |

DATA BUS

Address Bus and Relation to Memory Field

FIGURE 1.2

-7-

of memory. The high order 8 bits of the address (ADH) therefore indicates in which page the address is located, and the low order 8 bits (ADL) indicates a specific address on that page.

The first page in memory (ADH = 00) is referred to as page zero. The next higher order page (ADH = 01) is referred to as page 1, etc.

#### 1.1.4 System Components

The block diagram in Figure 1.1 shows the basic components which comprise all microcomputer systems. Each of these blocks may consist of one or more integrated circuits and, in fact, the functions may be combined into single chips. However, the basic operation of each remains the same.

#### 1.1.4.1 <u>Clock Generator</u>

The clock generator produces a continuous waveform which is normally used to control all signal transitions within the system. It acts as the "heart" of the system. In the typical microcomputer system the address bus will change during one half of the clock cycle and the data will be transferred during the second half. In addition to interpreting the address, data and control lines, the processor and support chips must also examine the system clock to know when to put out data or when to latch in data generated by another device.

#### 1.1.4.2 Program Memory

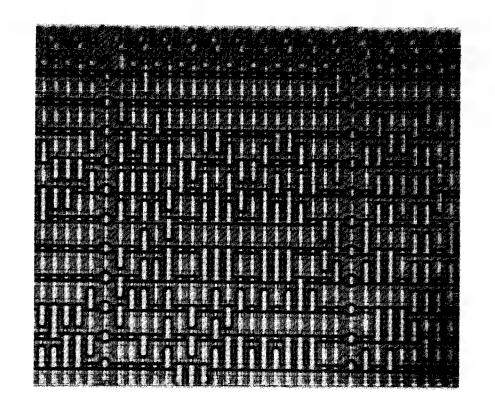

The program memory stores the sequence of instructions which comprises the system program. Like any memory, this unit puts a pattern of 1's and 0's on the data bus in response to the address on the address bus input. Each unique address selects a set of 8 binary bits and places this data on the data bus. Note that it does not matter where the address is generated or where the data is used; the memory simply obeys the rule that, given an address, it will put the corresponding 8 bits of data on the data bus.

A unique characteristic of most microprocessor-based systems is that the program is usually stored in "READ-ONLY" memories. The data is stored in a fixed pattern of bits in the memory. Figure 1.3 shows a section of a semiconductor READ-ONLY Memory (ROM).

-8-

Portion of Read Only Memory Matrix FIGURE 1.3

Since the data is stored in the physical configuration of the device, the data will not be lost when power is disconnected from the chip. In addition, it is only necessary to insert the device into its socket to provide the system program. The term "Read-Only Memory" refers to the fact that, in system operation, it is impossible for the processor to cause data to be stored in the device. The processor can only "READ" the data stored in the device during the manufacturing process. "READING" a memory involves the simple process of supplying an address to the device to obtain the corresponding 8 bits of data on the data bus.

#### 1.1.4.3 Data Memory

For temporary storage of input data, the results of arithmetic operations, etc., the microcomputer uses a Read/Write Memory, commonly referred to as a RAM (Random Access Memory). The processor can store data in the RAM (called "WRITING" the RAM), or it can read back the data it has stored. As in the ROM, each address corresponds to eight memory cells. However, in a RAM the data must be placed into the memory by the processor and is stored in cross-coupled latches. Turning off the power to the chip will cause the loss of all data stored there. The data is said to be

-9-

"volatile." Data in a ROM is not lost when power is disconnected from the device; the data is therefore referred to as "non-volatile."

"WRITING" data into a RAM takes place when the Write-Enable signal goes to the write state. At this time the data on the data bus will be stored into the eight memory cells corresponding to the address on the address bus. The processor can READ this same data by supplying the proper address and keeping the Write-Enable line in the Read state.

#### 1.1.4.4 Input/Output Devices

The Input/Output Devices are the circuits which interface the printer, keyboard, displays, etc. to the processor. These allow the processor to read data from the keyboard, to test the state of sensors and switches, and to display or to print the results of internal operations.

No matter where data is generated, it must be in the form of 1's and 0's before the processor can work with it. Likewise, actions to be initiated by the processor must be triggered by 1's and 0's transferred by the processor to a set of output lines.

The transfer of data from the processor to an output device is usually accomplished by "WRITING" the data out in much the same manner as the processor writes data into RAM. Each set of 8 input or output lines (referred to as "PORT") is given an address and the processor simply writes data to that address. For each "1" written out to the peripheral port an output is set high and for each "0," the corresponding output is set low.

Although the basic concept of peripheral control is simple, the actual implementation of these interfaces can involve many sophisticated techniques designed to allow the processor to maximize its ability to control peripherals and perform internal operations concurrently. These techniques are discussed in detail in Chapter 2 of this manual.

#### 1.1.4.5 The Microprocessor

At first glance it may seem strange to discuss the support chips in the microprocessor-based system before mentioning the processor. However, this approach is necessitated by the fact that most of the inputs and outputs on the processor are aimed at properly controlling the support chips and peripheral devices discussed above.

The address bus, the bi-directional data bus and the Write-Enable line allow the processor to exercise direct control over the rest of the system. The address bus puts out addresses to control the source or

-10-

destination of data transfers. These addresses are derived from various sources within the processor. During the fetch of instructions from program memory, the addresses are usually derived from a counter which controls execution of sequential instructions. Addresses for data transfers between the processor and RAM are usually derived directly from the program or are calculated from the data in the program and data in internal registers.

The bi-directional data bus serves as a path for transferring data into and out of the processors. The direction of the data transfer is determined by the Write-Enable line.

Another special function found in modern microcomputer systems is the interrupt. This function allows the peripheral devices to directly affect the operation of the processor. When the interrupt signal is generated, the processor usually completes its current instruction and then, under program control, will respond to the interrupt. The importance of this function is that it allows the processor to execute the system program without requiring the system program to monitor the status of the peripheral device. The software which handles the operation of each peripheral will be executed only when required.

#### 1.2 INTRODUCTION TO THE MCS650X MICROPROCESSOR FAMILY

The initial MOS Technology, Inc. microprocessor offering consists of the MCS6501, which is MC6800 compatible; the MCS6502, which has clock drivers onchip; and three 28-pin processors, the MCS6503, MCS6504, and MCS6505. All of these devices are aimed at a specific range of applications. Therefore, it is important to develop an understanding of the capabilities of each and the differences between them.

The MCS6501 has application in existing M6800 systems where conversion to the MOS Technology, Inc. processor is to be performed. This processor requires the full high-level two-phase clocks of the M6800 system. The MCS6502 is expected to find application in all new designs which require a full 16-bit address bus. However, in the small cost-sensitive system, the 28-pin processors can represent a savings in both processor cost and printed circuit board area. The MCS6503, MCS6504, and MCS6505 will find application in all new designs where the system will operate within the addressing limits.

#### 1.2.1 The MCS6501

The MCS6501 is the first member of the microprocessor family to be introduced. It is designed to be pin compatible with the M6800 and therefore conversion from the MC6800 to the MOS Technology, Inc. MCS6501 requires only that the system be reprogrammed. This allows the M6800 user to take full advantage of the software power (addressing modes, etc.) of the MCS650X processor family.

Although the conversion process is fairly simple, it is important to keep in mind the differences between the MC6800 and the MCS6501. The pins on the MCS6501 all do the same general function as those on the MC6800 but the function performed may differ somewhat in detail. Figure 1.4 contains a detailed, pin-for-pin comparison of these two processors. A thorough understanding of this table, along with an understanding of the MCS650X software will allow the system designer to perform the conversion with very little difficulty. The MCS6501 provides a full 16-bit address bus, 8-bit data bus and two interrupts.

-12-

|       | MOTOROLA | MOS TECHNOLOGY |       | MOTOROLA | MOS TECHNOLOGY |  |

|-------|----------|----------------|-------|----------|----------------|--|

| PIN # | 6800     | 6501           | PIN # | 6800     | 6501           |  |

| 1     | Vss      | Vss            | 21    | Vss      | Vss            |  |

| 2*    | Halt     | Ready          | 22    | A12      | A12            |  |

| 3     | Øl (in)  | Ø1 (in)        | 23    | A13      | A13            |  |

| 4     | IRQ      | IRQ            | 24    | A14      | A14            |  |

| 5*    | VMA      | VMA            | 25    | A15      | A15            |  |

| 6     | NMI      | NMI            | 26    | D7       | D7             |  |

| 7     | BA       | BA             | 27    | D6       | D6             |  |

| 8     | Vdd      | Vdd            | 28    | D5       | D5             |  |

| 9*    | AØ       | АØ             | 29    | D4       | D4             |  |

| 10    | A1       | A1             | 30    | D3       | D3             |  |

| 11    | A2       | A2             | 31    | D2       | D2             |  |

| 12    | A3       | A3             | 32    | D1       | D1             |  |

| 13    | A4       | A4             | 33    | DØ       | DØ             |  |

| 14    | A5       | A5             | 34    | R/W      | R/W            |  |

| 15    | A6       | A6             | 35    | N.C.     | N.C.           |  |

| 16    | A7       | A7             | 36    | DBE      | DBE            |  |

| 17    | A8       | A8             | 37    | Ø2 (in)  | Ø2 (in)        |  |

| 18    | A9       | А9             | 38*   | N.C.     | N.C.           |  |

| 19    | A10      | A10            | 39*   | TSC      |                |  |

| 20    | A11      | A11            | 40    | Reset    | Reset          |  |

|       |          |                |       |          |                |  |

#### \* DIFFERENCES

| PIN # | MOTOROLA 6800                                                                                          | MOS TECHNOLOGY 6501                                                                                                                                                                   |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2     | Halt - Stops processor after<br>completing current instruction.<br>Address Bus in off state.           | Ready – Stops Processor during<br>current instruction. Address<br>Bus reflects current address<br>being read.                                                                         |  |  |  |

| 5     | VMA - Signal determines when<br>address from processor is<br>Valid.                                    | VMA - No need for Valid Memory<br>Address Signal. All addresses<br>are valid at all times. This<br>pin is internally tied to Vdd<br>and can be used as a VMA signal<br>in high state. |  |  |  |

| 9     | Address Bus uses Tri-State<br>Output Buffers.                                                          | Address Bus uses TTL level<br>Output Drivers.                                                                                                                                         |  |  |  |

| 38    | No Connection                                                                                          |                                                                                                                                                                                       |  |  |  |

| 39    | T.S.C Three-State Control<br>Controls <b>a</b> ll Three-State<br>Buffers, Address Bus and<br>Data Bus. | N.C No need for TSC since<br>Address is not Three-State and<br>DBE Controls Three-State of<br>Data Bus.                                                                               |  |  |  |

## Pinout Comparison MOS TECHNOLOGY INC. MCS6501, MOTOROLA MC6800 FIGURE 1.4

## -13-

#### 1.2.2 The MCS6502

The second member of the processor family is a 40-pin device which provides all the features of the MCS6501, along with an "on-the-chip" oscillator and clock drivers. This device should be used in all new designs which require the capability of the 40-pin processors. The clock drivers can be driven with a single TTL level square wave or with the internal oscillator. The frequency of operation of the internal oscillator can be set by attaching an R-C combination to the chip and, if the clock stability is required, by attaching a crystal between the oscillator and ground. This feature totally eliminates the problems encountered in generating MC6800 type clock signals.

As in the MCS6501, the MCS6502 provides a full 16-bit address bus, 8-bit bi-directional data bus and two interrupts. In addition, the MCS6502 provides a sync signal which indicates those cycles in which the processor is fetching an operation code from program memory.

#### 1.2.3 The MCS6503, MCS6504 and MCS6505

Three 28-pin versions of the processor are available. These three differ in the number of address lines and the number of interrupts provided. Having all three options available allows the designer to tailor his processor to his particular application.

The MCS6504 provides a total of 13 address pins and can, therefore, address a full 8K bytes in its memory space. However, this part provides only one interrupt request input,  $\overline{IRQ}$ . The non-maskable interrupt ( $\overline{NMI}$ ) is not included in the pinouts of this device.

The MCS6503 and MCS6505 provide one less address line. In the MCS6503, this address line is replaced with a second interrupt input,  $\overline{\text{NMI}}$ . In the MCS6505, this address line is replaced by the RDY signal. All other functions on these processors are the same. The details of each of these pins are discussed in the following sections.

The operation of the various busses, control signals, etc. is exactly the same on all MCS650X products with all processors obeying the system specifications discussed in Section 1.3 of this manual.

#### 1.3 MCS6500 SYSTEM CONCEPTS

#### 1.3.1 Bus Structure

The MCS6500 microcomputer system is organized around two primary busses. Each bus consists of a set of parallel paths which can be used to transfer binary information between the devices in a system. The first bus, known as the ADDRESS BUS, is used to transfer the address generated by the processor to the address inputs of the memory and peripheral interface devices. The processor is the only source of addresses in a normal system, so this bus is referred to as "unidirectional." The address bus consists of 16 lines on the MCS6501 and MCS6502. This allows the processor to access (READ or WRITE) up to a total of 65,536 memory words, registers, etc. In the MCS6503, MCS6504, and MCS6505, the address bus contains fewer lines; therefore, they operate with a smaller "address space." This is discussed in detail in Section 1.1.3.

The data bus in the MCS6500 microcomputer system consists of an 8-bit bi-directional data path. These lines transfer data from the processor to the selected memory word, etc. during a WRITE operation and from memory into the processor during a READ operation. All data and all instructions are transmitted on the data bus.

The direction of the data transfers is controlled by the READ/WRITE (R/W) line on the processor. This line performs the Write Enable function described in Section 1.1.4.3. As long as the R/W line is high (> 2.4V DC), all data transfers will take place from memory to the processor (READ operation). This line will go low only when the processor is going to WRITE data out to memory.

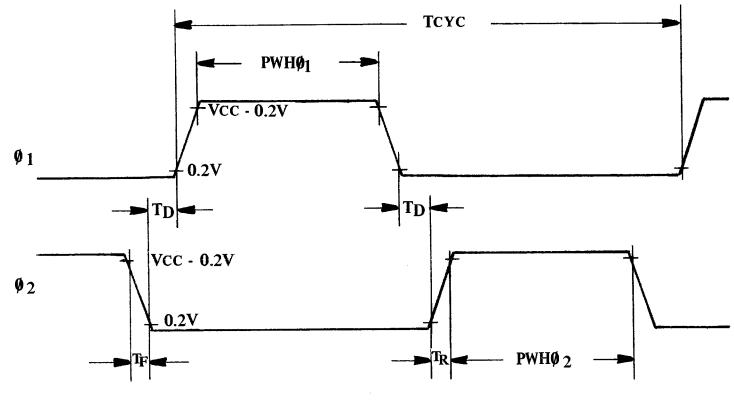

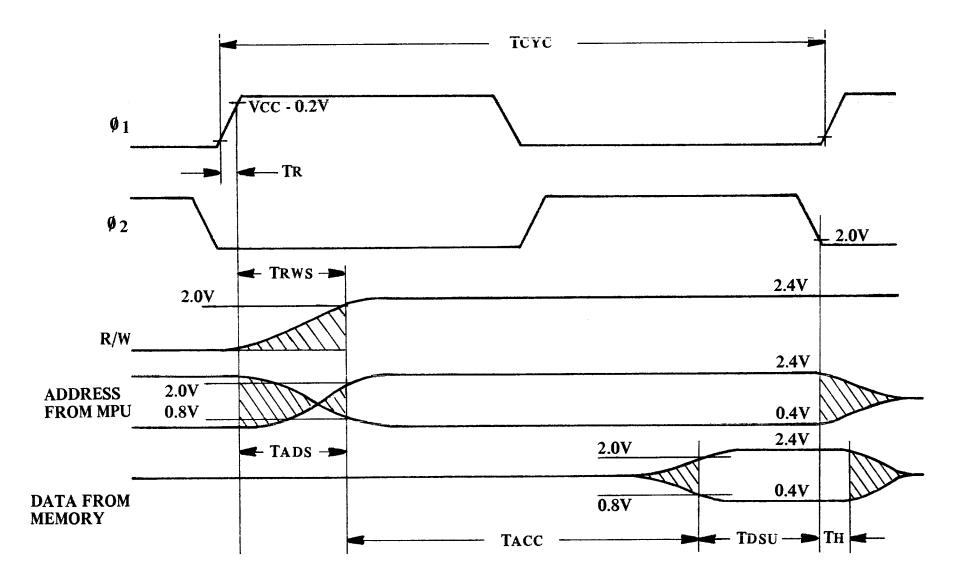

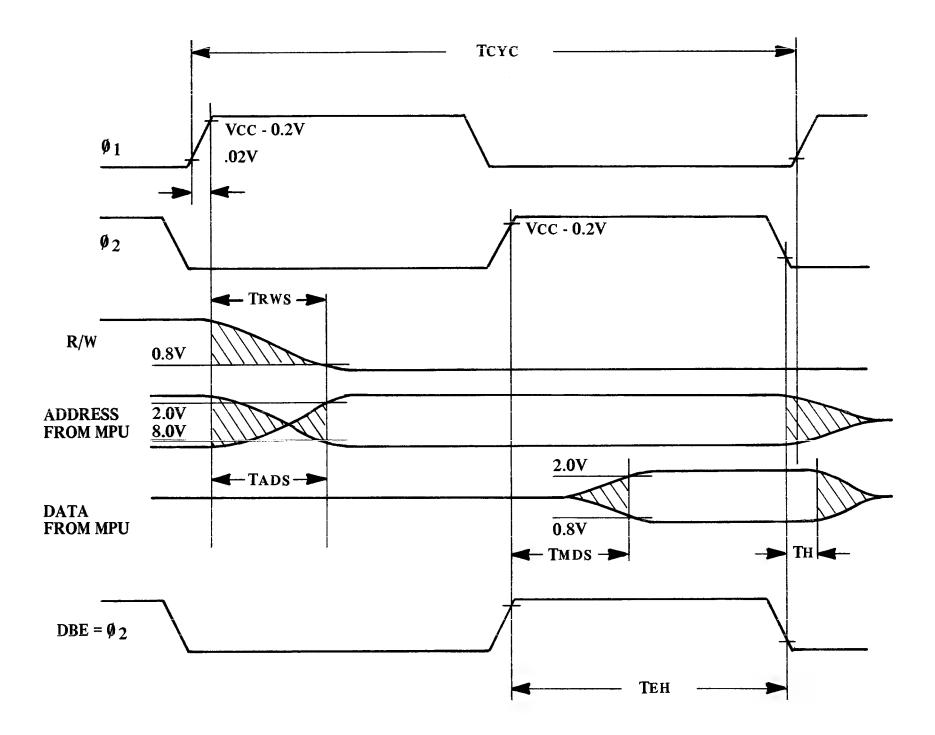

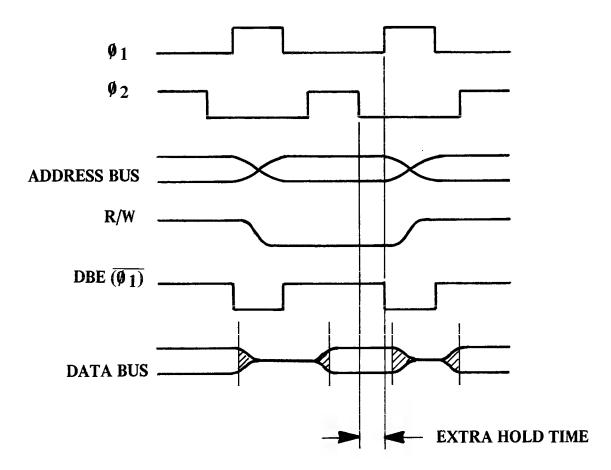

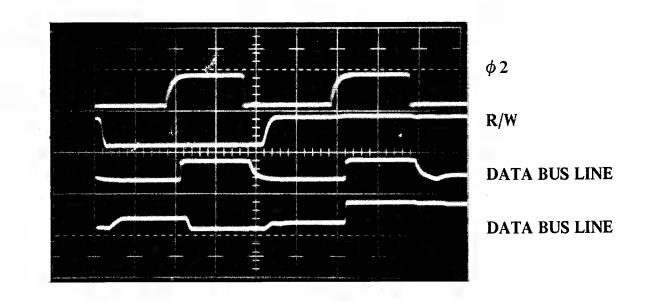

As in most microcomputer systems, the timing of all data transfers is controlled by the system clock. The clock itself is actually two nonoverlapping square waves. This two-phase clock system can best be thought of as two alternating positive-going pulses. This text will refer to the clocks as Phase One and Phase Two. A Phase One clock pulse is the positive pulse during which the address lines change and a Phase Two clock pulse is the positive pulse during which the data is transferred. The timing of the signals on the Address Bus, Data Bus, and R/W line are shown in Figures 1.5 through 1.8. All signal transitions are specified with respect to the Phase One and Phase Two clock signals.

-15-

In particular, the address lines and the R/W line will stabilize during Phase One, and all data transfers will take place during Phase Two.

The specific timing specifications for operating at a 1 MHz clock rate are also given in Figure 1.5. Note that the sequence of operations will be the same for all processors. However, these timing specifications will change for devices which are specified to operate faster than 1.0 MHz. The address is guaranteed to be stable 300 nanoseconds after the leading edge of Phase One, and the data must be stable 100 nanoseconds before the trailing edge of Phase Two. At 1.0 MHz operation, this allows the memory devices approximately 575 ns to make data available on the data bus. Although there are many factors which determine the actual data and address generated within the system, it is important to keep in mind that the basic operation shown in Figures 1.6, 1.7 and 1.8 does not change. These figures specify the system bus discipline which applies to <u>all</u> MOS Technology, Inc. processors and support chips.

#### 1.3.2 Processor Interrupts

Through the generation of processor interrupt signals, the peripheral devices (printers, keyboards, etc.) can request service from the processor. Although this technique is relatively simple in concept, the proper generation and control of interrupts is one of the most important problems which the designer will face. Total system capability can be greatly expanded if the processor is required to execute the peripheral software only when it is absolutely necessary. This is the goal of a wellplanned interrupt structure. The interrupt structure is very much a systems sophistication problem since it is the entire system which must properly respond to the interrupt inputs. In fact, the actual signals to which the system must respond are usually applied to the inputs of a peripheral interface device. In this device, the interrupts are enabled, disabled and latched until the interrupt is processed. The peripheral interface device generates signals which meet the requirements of the processor interrupt inputs.

There are two interrupt input lines to the microprocessor,  $\overline{IRQ}$  (Interrupt Request) and  $\overline{NMI}$  (Non-Maskable Interrupt).

Since the requirements of the two interrupt inputs differ, they will be discussed separately below. The response of the processor to these inputs is very similar, however, after the interrupt is recognized. For this

-16-

| CHARACTERISTIC                                          | SYMBOL                          | MIN.       | TYP. | MAX. | UNIT |

|---------------------------------------------------------|---------------------------------|------------|------|------|------|

| Cycle Time                                              | <sup>Т</sup> сүс                | 1.0 µs     |      |      | µsec |

| Clock Pulse Width Ø1<br>(Measured at Vcc-0.2v) Ø2       | PWH Ø1<br>PWH Ø2                | 430<br>430 |      |      | nsec |

| Rise and Fall Times<br>(Measured from 0.2V to Vcc-0.2V) | T <sub>F</sub> , T <sub>R</sub> |            |      | 25   | nsec |

| Delay time between Clocks<br>(Measured at 0.2V)         | T <sub>D</sub>                  | 0          |      |      | nsec |

| CHARACTERISTIC                                                                                          | SYMBOL           | MIN. | TYP. | MAX. | UNIT |

|---------------------------------------------------------------------------------------------------------|------------------|------|------|------|------|

| Read/Write Setup Time from MCS650X                                                                      | T <sub>RWS</sub> |      | 100  | 300  | ns   |

| Address Setup Time from MCS650X                                                                         | T <sub>ADS</sub> |      | 200  | 300  | ns   |

| Memory Read Access Time T <sub>R</sub><br>T <sub>CYC</sub> - (T <sub>ADS</sub> - T <sub>DSU</sub> - tr) | TACC             |      |      | 500  | ns   |

| Data Stability Time Period                                                                              | <sup>T</sup> DSU | 100  |      |      | ns   |

| Data Hold Time                                                                                          | T <sub>H</sub>   | 10   | 30   |      | ns   |

| Enable High Time for DBE Input                                                                          | T <sub>EH</sub>  | 430  |      |      | ns   |

| Data Setup Time from MCS650X                                                                            | T <sub>MDS</sub> |      | 150  | 200  | ns   |

Clock and Read/Write Timing Table (1MHz Operation)

FIGURE 1.5

Two Phase Clock Timing FIGURE 1.6

Timing for Reading Data from Memory or Peripherals FIGURE 1.7

reason, the internal operation of the processor during interrupt servicing is discussed in the detailed analysis of the processor chip. Instead, this section will concentrate on the system level considerations which are required to assure proper operation of the interrupt structure.

#### 1.3.2.1 Applications for Interrupts

One of the most important tasks facing the microcomputer system designer is the determination of those signals which will cause processor interrupts and those operations which will take place in response to these interrupts. A detailed discussion of these considerations is included in Chapter 2 of the manual; however, a few examples of interrupt-driven operations will be presented here to help the designer develop an understanding for why this technique is used extensively in microcomputer systems.

#### Example 1--A Fully-Decoded Keyboard

The problem of data entry is solved in many systems by a keyboard. In small systems, the interpretation of the binary code associated with each key can be determined by the processor. However, in large data terminals, the keyboard usually includes an encoder which generates the unique code corresponding to each key. When a key is closed, the corresponding code is placed on the output pins and a strobe signal is generated to indicate that a key has been pressed.

The keyboard represents a perfect candidate for interruptdriven operation. The interrupts occur relatively infrequently and the operation to be performed is relatively simple. The keyboard strobe line is connected directly to an interrupt input on a peripheral interface device. Each time a strobe signal is generated, an interrupt occurs, the processor reads the data on the peripheral port into memory, analyzes this data and then returns to the program that was in process. If no keys are pressed, the processor spends no time at all in servicing the keyboard.

Without the interrupts, the processor would have to read the keyboard data into memory periodically in order to detect an active key. This operation would be performed about every fifty to one hundred milliseconds. In addition to detecting an active key, the processor must make sure that each separate activation of a key is detected once and only once. This is discussed in Sections 1.3.2.5 and 1.3.2.6. This software is much more complex than the simple interrupt routine. Another drawback of noninterrupt processing is that the processor is required to spend a periodic

-20-

portion of its time on the keyboard. In many systems, this is not a problem, but in large terminals, etc., the time spent checking for keyboard strobes could be better spent in other operations. The designer must, therefore, ask himself if the system under development is such that the processor can perform the keyboard strobe checking function while still completing its other tasks.

#### Example 2--A Scanned Display

Although time is a major factor in determining the necessity of interrupts, the interrupt technique can also be extremely useful when performing parallel operations. A prime example of this can be found in a system which contains a digital display and/or printer.

A digital display is usually "scanned" such that each digit is driven for a short period of time in sequence. The entire display is scanned at a rate which the eye cannot detect. However, it can be noted here that the display requires scan-related attention from the processor at fixed intervals. It is very difficult for the processor to calculate repetitive time intervals while it is performing its normal system program routines. The processor would much prefer to run the system program without consideration for the display time intervals, only executing the display software when it is required.

A solution to the above problem is the generation of processor interrupts at fixed intervals using an external counter or clock. Each time an interrupt occurs, the data for the next digit in the display is placed on an output port. The processor then returns to the program it had been executing.

Both of the operations described above represent solutions to system problems. Events which happen very infrequently and events which must be performed in parallel with other events or in parallel with the main system program should be seriously considered as candidates for interrupts. Additional considerations are described in Chapter 2 of this manual; however, it is important to note here that the typical system may have several sources of interrupts, each with its own timing and each with its own set of operations which must be performed in response to the interrupts.

-21-

#### 1.3.2.2 Interrupt Prioritizing

After a careful analysis of the total system and a determination of all the sources of interrupts, the designer must ask himself, "What happens if more than one interrupt source requires attention at one time?" A priority level must be established between the various interrupt sources. Which ones must be taken care of within a very short period? Which ones can be put off for a while? This prioritizing and the technique for selecting among several concurrent interrupts is very important to the system operation and should be established early in the system development process.

The MCS650X-based system can employ several hardware methods of determining the highest priority active interrupt. These usually involve using a special "priority encoder" which allows the processor to go directly to the software which services the highest priority interrupt. After this is complete, it will go to the next higher priority and execute that software. However, the MCS650X family provides a much less expensive method of interrupt prioritizing. This is the "polled" interrupt. With this technique, each time an active interrupt source is detected, the processor executes a "polled" interrupt program that interrogates the highest priority interrupt, then the next highest and so on until an active interrupt is located. The program services that interrupt and returns to the "polled" interrupt program and continues to interrogate the next highest priority interrupt until all have been interrogated or clears the interrupt disable to allow nested interrupts. The "polled" interrupt program is always executed when an interrupt occurs so that all interrupts that occur concurrently will be serviced in order of priority level.

Several hardware techniques for prioritizing interrupts are discussed in Chapter 2 of this manual. The next section, however, describes the system interconnect which allows use of the simple "polled" interrupt.

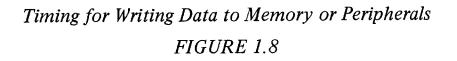

#### 1.3.2.3 System Interconnect for Interrupts

In the simple "polled" interrupt technique for prioritizing interrupts, the interrupt software actually determines the highest priority active interrupt. The  $\overline{IRQ}$  or  $\overline{NMI}$  interrupt request signals simply cause the processor to jump to the polling software.

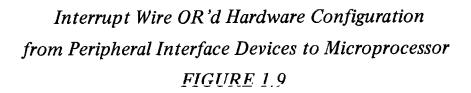

For this reason, it is possible to "OR" the various interrupt signals together to form the signal for the processor. Any active interrupt source will then cause the processor to do the interrupt polling and

-22-

servicing operation. Provision for generation of this OR function is provided in the MCS6500 family peripheral interface devices. Since these peripheral adapters perform many of the enabling and latching functions necessary for proper interrupt servicing, the peripheral adaptor interrupt output then provides the actual signal which interrupts the processor. These interrupt outputs can be "WIRE-OR'd" by connecting them all together and then connecting this single line to the processor. This input should then be pulled to +5V with a resistor. Any one of the interrupt outputs on the peripheral adaptors can then pull this interrupt low. This simple configuration is shown in Figure 1.9.

#### 1.3.2.4 Interrupt Servicing

Although a great deal has been said previously about the process of establishing interrupts and determining just what happens in response to an interrupt, it would be useful to detail the sequence which takes place when an interrupt is recognized by the processor. This will establish a basis for understanding of the details of the processor interrupt inputs.

An interrupt request is signaled by a GND (< 0.4V) signal on the interrupt request input. This interrupt will be recognized after the processor completes the instruction which it is currently executing. The next step is to store enough of the contents of the internal processor registers to assure that the processor can resume execution of the program which was interrupted. In particular, the Program Counter and the Processor Status Register are stored in a series of memory locations specified by another internal register, the Stack Pointer. As discussed in Chapter 9 of the Programming Manual, saving the contents of the Program Counter and Processor Status register uniquely defines, in memory, the state of the microprocessor at the time the interrupt occurred. The processor then goes to two fixed locations in memory to determine the address low and address high of the interrupt software.

The operation to this point is automatic and is determined by the internal processor logic. After the processor has properly set the address bus, execution of the interrupt program commences. Everything which occurs subsequently is determined by the system software.

The total interrupt software described above will consist of a complex combination of polling and interrupt servicing routines. However, unless

-23-

•

a hardware prioritizing scheme is used, the actual system interconnections will not become any more complex than that shown in Figure 1.9.

### 1.3.2.5 Interrupt Request (IRQ)

As stated in Section 1.3.2, the two interrupt lines for the microprocessor are  $\overline{IRQ}$  and  $\overline{NMI}$ . The requirements for proper operation of the maskable Interrupt Request input (IRQ) are more stringent than for the second interrupt input,  $\overline{NMI}$ . This is due primarily to the fact that  $\overline{NMI}$ is edge-sensitive. With the  $\overline{IRQ}$  input, the processor will be interrupted any time the signal on  $\overline{IRQ}$  is GND (< 0.4V) and the internal Interrupt Disable flag is cleared. The Interrupt Disable flag (I) is a single bit in the internal Processor Status Register. The details of this register are described in Section 3.2 of the Programming Manual.

In the processing of interrupt request from the  $\overline{IRQ}$  input, the I flag is extremely important. This is the element which assures that an interrupt will be recognized and serviced only once for each request and only when an interrupt is desired. This is described in detail below.

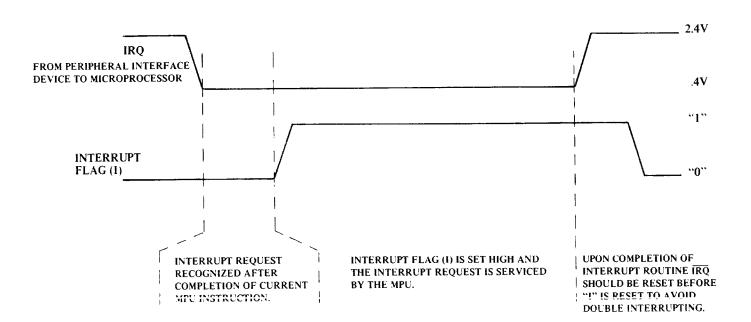

Figure 1.10 details the sequence of operations which should take place during the servicing of an  $\overline{\text{IRQ}}$  interrupt. A positive or negative transition of the signal from the peripheral device (printer, keyboard, etc.) is detected on the edge-sensitive inputs to the peripheral interface device. If the interrupt is enabled within the peripheral interface device, the interrupt request output ( $\overline{\text{IRQ}}$ ) on this chip will go low. The interrupt condition is latched within the peripheral interface device to allow sufficient time for the processor to poll the interrupt sources, assuring that the interrupt signal will not be cleared before the polling can be completed. This latch is reset by the processor as it executes the software associated with that interrupt. Details of this operation are described in Section 1.4.1.2.10

The Interrupt Disable flag (I) is set automatically when the processor recognizes an interrupt. This assures that this same interrupt will not be recognized again. Resetting this flag can be performed manually with an instruction in the program or automatically with a "Return from Interrupt" instruction. It is very important that "I" not be cleared before the interrupt input is reset. Performing the "Clear I" instruction too early in the program can cause this same interrupt to be recognized again.

-25-

The processor will then proceed to service this as if it were a new interrupt.

### 1.3.2.6 Non-Maskable Interrupt (NMI)

The NMI input to the processor is edge-sensitive. To cause an interrupt to occur, there must be a negative transition of the signal on the  $\overline{\rm NMI}$  input. This negative transition will cause a single interrupt to occur. After servicing the interrupt, the processor will ignore this input until the  $\overline{\rm NMI}$  signal goes high (> +2.4V) and then back to ground.

The response to an MMI interrupt signal cannot be disabled within the processor. After the processor completes the instruction being executed, it will recognize the interrupt and will proceed to service the interrupt as described in the previous section. The proper discipline to employ in all interrupts is for the interrupt signal to be latched until the processor completes servicing the interrupt. This method of operation is assured if all the interrupts are connected to the interrupt inputs of the peripheral interface devices in the family.

Processing of multiple interrupts in a polled interrupt structure requires that all of the interrupts be polled before executing a "Return from Interrupt" instruction. This is necessitated by the "WIRE-OR" technique for combining the interrupts, since no knowledge exists of which line went to ground. If one of the interrupts is left unserviced, it will hold the NMI signal to ground, disabling the interrupts from all other sources since it is necessary for the NMI signal to go high (> 2.4V) and back low again for an interrupt to occur. This is not true for the IRQ input since this latch is level-sensitive. Performing a "Return from Interrupt" before all IRQ interrupt sources are serviced will simply cause another IRQ interrupt to occur.

### 1.3.3 System Reset

One of the basic system control functions is the system RESET signal. Whether this signal is generated automatically by external power-on circuitry or manually from a push-button switch, the system components must obey a fixed set of rules to assure proper system operation. This is particularly true for the peripheral interface devices.

-27-

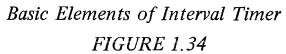

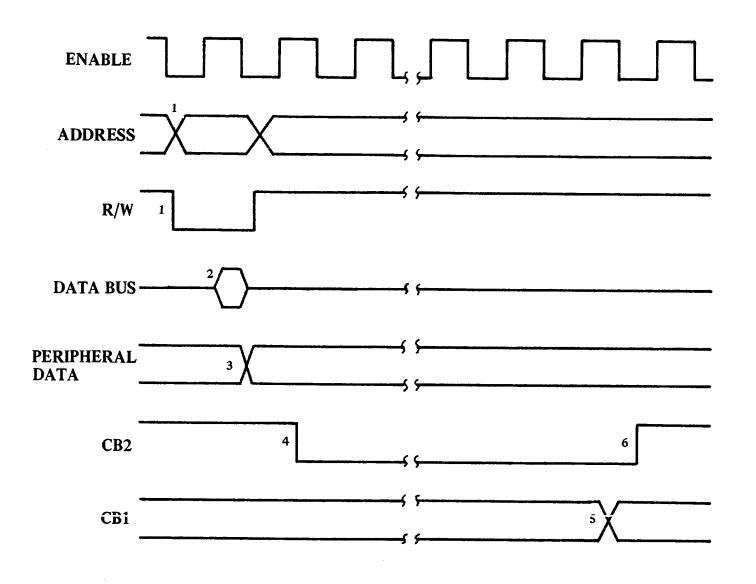

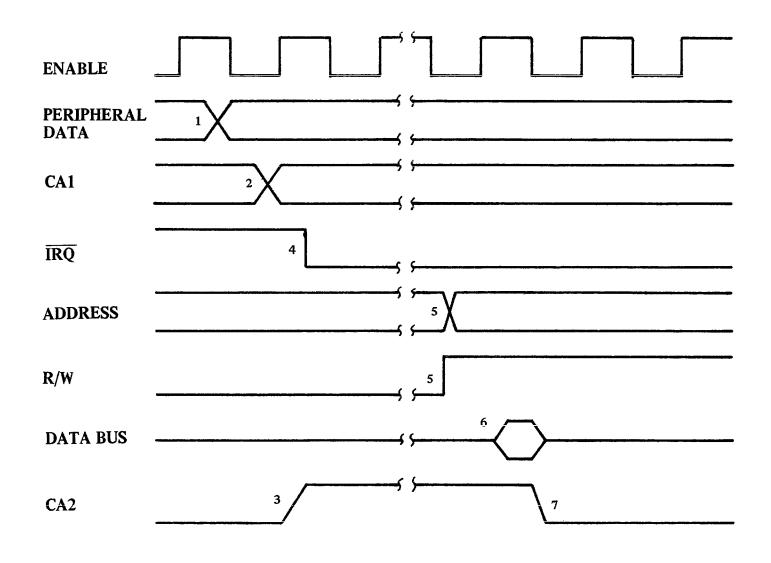

In the MCS650X-based systems, an assumption is made that RESET pins on all peripheral interface devices and on the processor will be held low during power-on until the supply voltages and the clocks have stabilized. This procedure assures that the peripheral pins will remain in a known state until the entire system is initialized and the processor is ready to assume control of the output lines, i.e., is ready to run the system program.